Other Parts Discussed in Thread: SYSCONFIG, DP83869

Tool/software:

Hi Aaron,

Following your guidance in the above post, I did the test.

1 The link polarity is taken care when Enhanced Link is enabled. You can also disable Enhanced Link and see if you're able to scan for the device (which will point out whether the issue is with Enhanced Link configuration)

--I have test two kinds of Ethernet cable in case of the link polarity, I also disable Enhanced link in Sysconfig to test, and failed to scan my board.

2 tiesc_addOnBoardResetSequence() logic is implemented - which you already have taken care of.

--confirm this

3 tiesc_ethphyInit() logic has been modified to use DP83826 PHY and corresponding mods, instead of DP83869 PHY.

--do nothing here

4 There is a strapping issue in our ICSSG0 add-on board for which a software workaround is implemented in tiesc_ethphyEnablePowerDown() API. You can remove this if this issue is not applicable in your case.

--I haven't met strapping issue by now, keep this tiesc_ethphyEnablePowerDown() here could cause something wrong?

Couple of things to check here is:

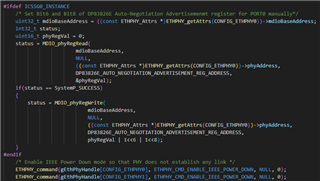

Are you able to access the PHY registers through MDIO?

-- Yes I can. I wrote CR1 and CR2 reg of the PHY and can read state_reg of the PHY.

Are you getting a link change status in the MDIO link register, that is, 0x30010E40 (base addresses for MDIO emulated space) if you're using MDIO firmware workaround (MDIO_MANUAL_MODE_ENABLED) or 0x3003240C if you're not using MDIO emulation?

--do you are meaning access 0x30010E40/0x3003240C in CCS by Memeory Browser? I read them in Memeory Browser, and both are 0. MDIO_MANUAL_MODE_ENABLED is checked in my Sysconfig.

Is the firmware receiving EtherCAT frames? This can be confirmed by monitoring 0x30010E00 to 0x30010E03 Vendor Specific ESC Registers:

-- the link is not established, there is no EtherCAT frame.

BR,

CHunyang