Part Number: MCU-PLUS-SDK-AM243X

Other Parts Discussed in Thread: DP83869, DP83826E, SYSCONFIG

Tool/software:

Hi Ti Expert,

We are using our own designed board with EtherCat, and the Phy are DP83826 with its strapping configuration, connected to ICSSG0.

Now my problem is that How would I modify the Syscfg file from EtherCAT SubDevice Beckhoff SSC Demo to fit for our own board.

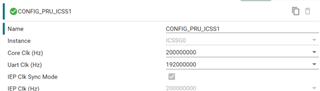

Firstly, I modified ICSS Instance from ICSSG1 to ICSSG0

Then, I went to ETHEPHY Configuration->ETHEPHY Device. DP83869 is the default. Should I keep here DP83869 or I should select None/Custom?

If I choose Custom, what is the next step?

As the following link mentioned, you have already done this test.

Could you please share the detailed instruction to me?

My SDK: ind_comms_sdk_am243x_09_02_00_24 ; CCS: 20.0.1.4__1.6.1

Thanks,

Chunyang