Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi Ti Expert,

Continue the following post.

Our own designed board's hardware are like this: ICSSG0 + two DP83826 for EtherCAT; CPSW0 + two DP83867 for EtherNet.

These EtherCat and EtherNet could work together on one single R5 core is what I am after.

I am trying to merge the following two project that could both work well with my board and CCS,

ind_comms_sdk_am243x_11_00_00_08\examples\industrial_comms\ethercat_slave_beckhoff_ssc_demo\am243x-evm\r5fss1-0_freertos -- my project base on this demo.

ind_comms_sdk_am243x_11_00_00_08\mcu_plus_sdk\source\networking\enet\core\examples\lwip\enet_lwip_cpsw\am243x-evm\r5fss0-0_freertos

the following are process I went, and where I was stuck.

1, import ethercat_slave_beckhoff_ssc_demo_am243x-evm_r5fss0-0_freertos_ti-arm-clang build OK

2 Copy sysconfig from ethercat_slave_beckhoff_ssc_demo_am243x-evm_r5fss1-0_freertos_ti-arm-clang build OK

3 In sysconfig: add Enet(CPSW), EthPhy(CPSW/ICSS) would be added automatically. Modify the EthPhy device to DP83867 both. And copy the Include Option from enet_Lwip_cpsw project. build OK

4 From enet_Lwip_cpsw demo, copy all the related files(.c and .h) and folderextPhyMgmt to local. Except Main.c which is from ethercat_slave_beckhoff. Add ENET_ENABLE_PER_CPSW=1 to Predefined Symbols, Build OK

5 add following to main.c

#include "ti_drivers_open_close.h"

#include "ti_board_open_close.h"

Build OK

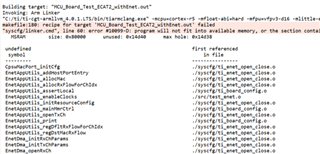

6 When I try to call enet_lwip_example() there are errors as following

After modify linker.cmd, the MEM error is fixed. but the "undefined symbol'", "first referenced" I have no idea how to fix them.

-------------------------------------------------------------------------------------------------------

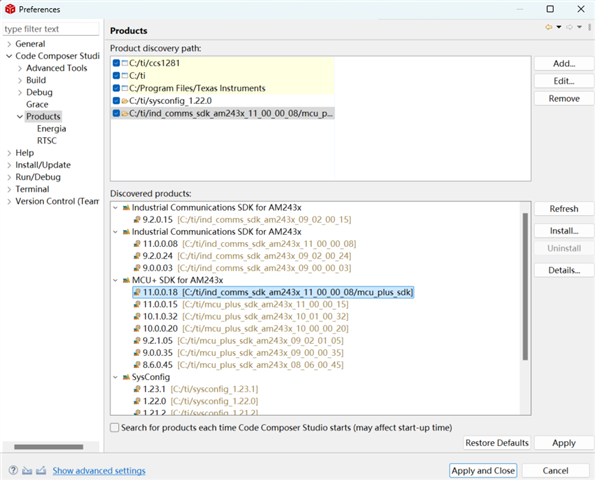

I had added ${SDK_INSTALL_PATH}/mcu_plus_sdk path to "Product discovery path" in CCS (from Window->Preferences->Code Composer Studio->Products).

The following are the include of my project, which merge the include from both enet_lwip_cpsw and ethercat_slave_beckhoff_ssc_demo two demo project.

Please help me with this!

BR,

Chunyang