Tool/software:

I've got a new product in the aerospace domain that's using the AM2434 chip (field-securable variant). Due to certification constraints, we've opted to disable the DMSC via performing the Secure Handover operation. As such, we now get to write our own drivers for system control functionality. I understand this is not TI's recommendation.

Currently I'm trying to enable the DDR interface for a custom SBL and am running into puzzling behavior. Following the TRM, AM243x SDK, and TI GEL files, I've been able to replicate the MPU, PLL, and PSC controllers to start enabling system hardware. The problem is the LPSC controller for the EMIF_CFG_0 module domain. I can enable all power/module domains in the chip EXCEPT that one. I can even enable the EMIF_DATA_0 module, despite the TRM claiming that I can't enable it until the EMIF_CFG_0 domain is enabled.

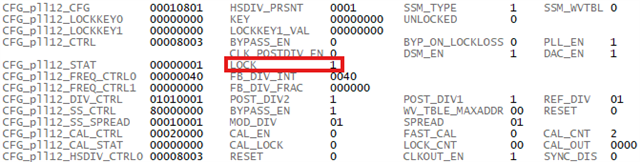

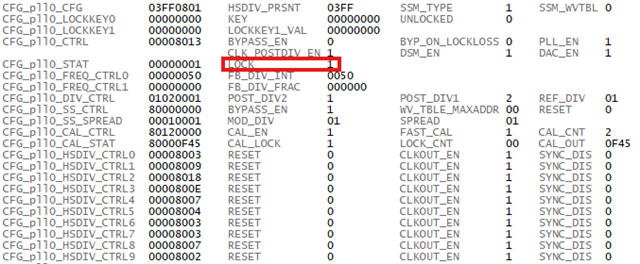

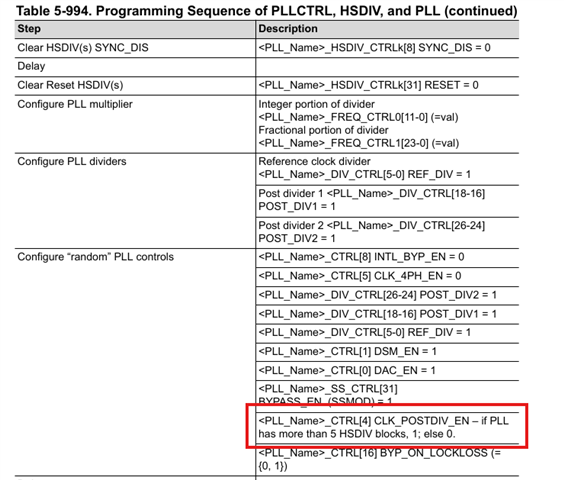

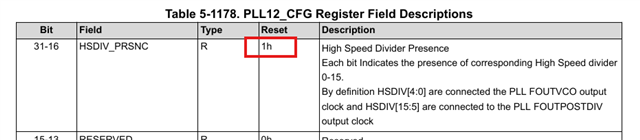

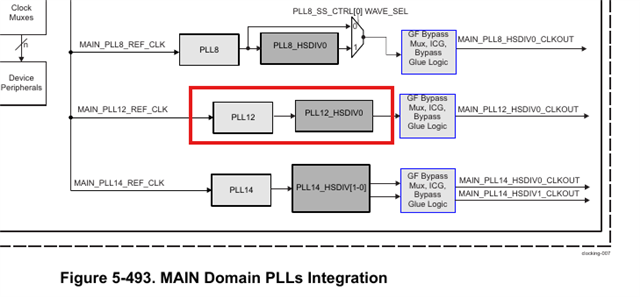

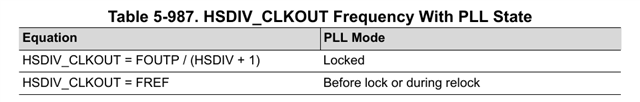

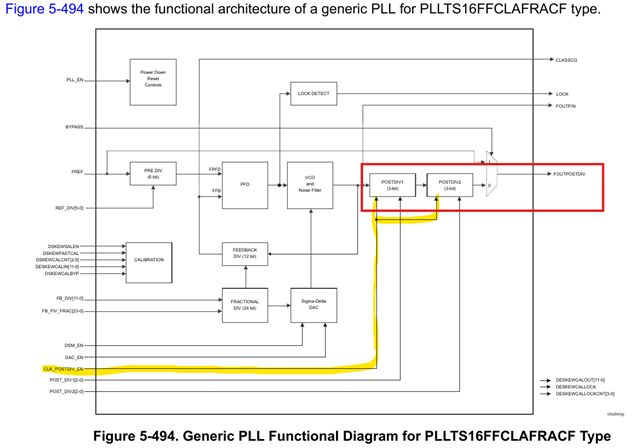

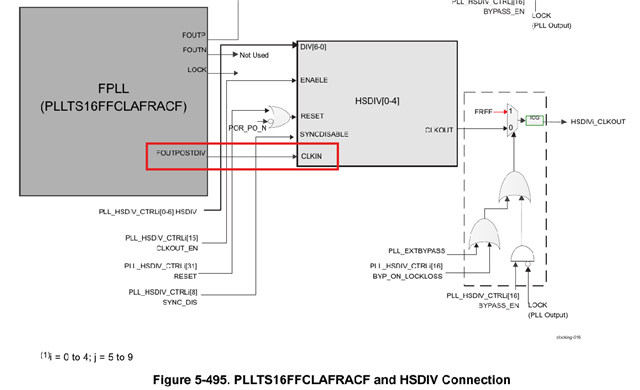

I configure the settings for the power transition, issue the GO command, and get hung up waiting for GOSTAT to clear. To reiterate, this same driver works fine for all other module domains.I've enabled/configured all the PLLs in the system (except MCU) according to the TI GEL files (AM24_PLL_PARAMS_OFC1.gel), which I understand is a dependency of using the LPSC module correctly due to auto-clock gating functionality.

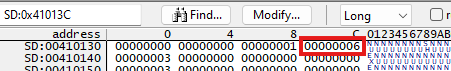

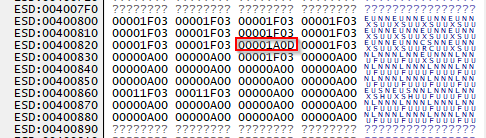

What I observe in the system MD_STAT register block is that all module domains I configure end up in a "good" state 0x1F03, but the EMIF_CFG_0 domain ends up at 0x1A0D, which doesn't appear to mean anything according to the listed enum values in the SDK.

What am I missing here? It feels incredibly odd that I can enable the EMIF_DATA_0 domain but not the CFG domain. By all appearances these two are linked together so meeting the "turn on" dependencies of one should enable the other.