Tool/software:

Hi Experts,

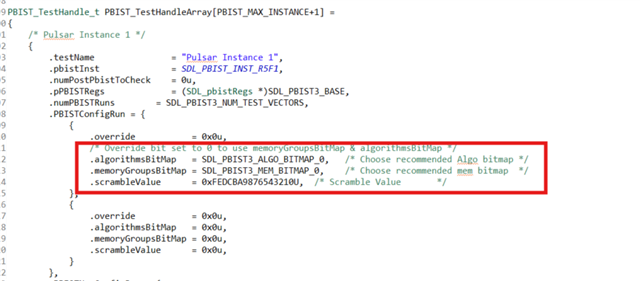

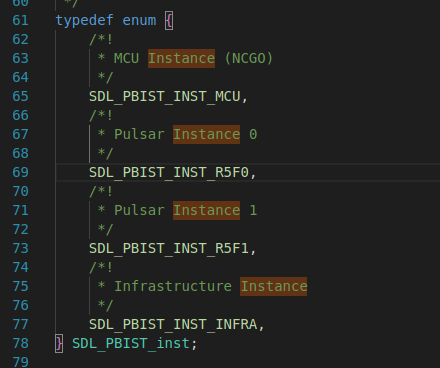

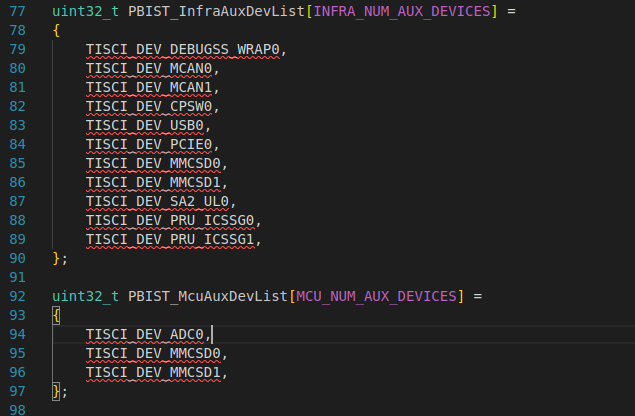

Our team is working towards utilizing TI SDL modules to satisfy functional safety requirements. Can you help me get more documentation regarding the SDL submodules. In the TRM there is information on only few modules (DCC, MCRC ). For example, how to know which memory regions are tested for different PBIST Test instances? Can we configure different memory regions?

Thanks,

Prithvi