Part Number: RM48L952

Other Parts Discussed in Thread: HALCOGEN, TMS570LC4357

Tool/software:

Hi,

I'm trying to get SPI1 to work with DMA. So far I can't see any bytes transmitted over the MOSI line with scope, only dummy bytes are being transferred when tested, so SPI is supposedly configured correctly.

I've tried to use the following sources in order to adapt to RM48L952 MCU with SPI1 (the example is with SPI3 RX):

- Big-endian address : #define SPI1_TX_ADDR ((uint32_t)(&(spiREG1->DAT1)) + 2U)

dmaReqAssign(DMA_CH0, 1); /* Request line 1: SPI1 Transmit */

etc.

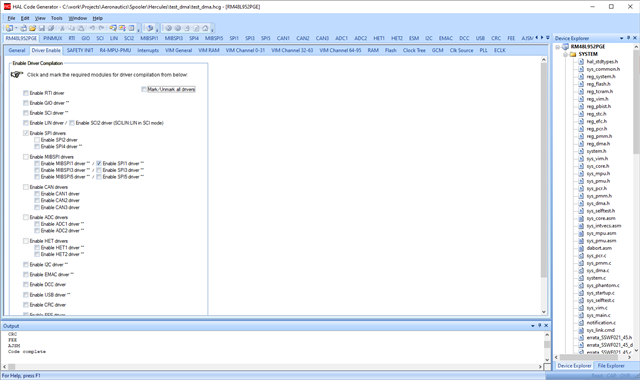

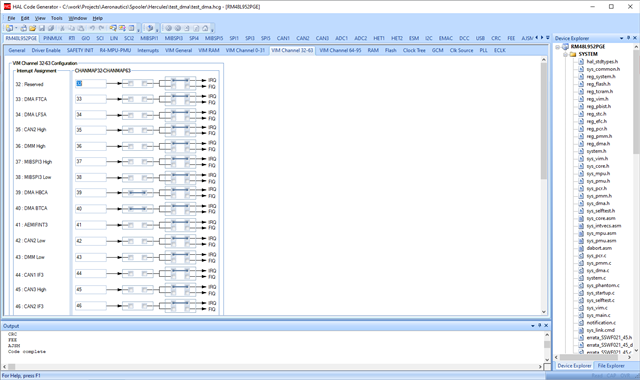

Attaching my test code and HALcogen configuration:

/** @file sys_main.c

* @brief Application main file

* @date 11-Dec-2018

* @version 04.07.01

*

* This file contains an empty main function,

* which can be used for the application.

*/

/*

* Copyright (C) 2009-2018 Texas Instruments Incorporated - www.ti.com

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/* USER CODE BEGIN (0) */

#define SPI_DMA_REQ_ENA (1U << 16) // Bit 16 enables DMA request in INT0 register

#define SPI1_TX_ADDR ((uint32_t)(&(spiREG1->DAT1)) + 2U)

/* USER CODE END */

/* Include Files */

#include "sys_common.h"

/* USER CODE BEGIN (1) */

#include "spi.h"

#include "sys_dma.h"

uint16_t spi_test_data[8] = {

0x1111, 0x2222, 0x3333, 0x4444,

0xAAAA, 0xBBBB, 0xCCCC, 0xDDDD

};

unsigned int SPI1_HBCFlag = 0;

unsigned int SPI1_BTCFlag = 0;

g_dmaCTRL g_dmaCTRLPKT_TX;

void dmaConfigCtrlTxPacket(uint32 sadd, uint32 dadd, uint16 dsize, uint16 BlockSize);

/* USER CODE END */

/** @fn void main(void)

* @brief Application main function

* @note This function is empty by default.

*

* This function is called after startup.

* The user can use this function to implement the application.

*/

/* USER CODE BEGIN (2) */

/* USER CODE END */

int main(void)

{

/* USER CODE BEGIN (3) */

/* Enable CPU Interrupt through CPSR */

_enable_IRQ();

spiInit();

spiREG1->PC0 = 0

| (1<<11) //SOMI[0] as functional pin

| (1<<10) //SIMO[0] as functional pin

| (1 << 9) //CLK as functional pin

| (0); //CS as GIO pin

spiREG1->PC1 = 0x01; //CS[0] as output

spiREG1->PC3 = 0x00; //CS[0]=0

// spiREG1->FMT0 &= ~(0x1FU);

// spiREG1->FMT0 |= 0x0FU; // 16-bit data

// Enable DMA controller

dmaEnable();

// dmaEnableInterrupt(DMA_CH0, FTC);

dmaEnableInterrupt(DMA_CH0, BTC); //Block transfer complete

dmaEnableInterrupt(DMA_CH0, HBC); //Half block transfer complete

// Map SPI1 TX to DMA CH0

/* Request line 0: SPI1 Receive */

/* Request line 1: SPI1 Transmit */

/* Request line 14: SPI3 Receive */

/* Request line 15: SPI3 Transmit */

dmaReqAssign(DMA_CH0, 1);

/* - configuring dma TX control packets */

dmaConfigCtrlTxPacket((unsigned int)&spi_test_data, SPI1_TX_ADDR, 1, sizeof(spi_test_data));

dmaSetCtrlPacket(DMA_CH0, g_dmaCTRLPKT_TX);

// Enable DMA channel

dmaSetChEnable(DMA_CH0, DMA_HW);

// // Enable SPI DMA request generation

spiREG1->GCR1 = (spiREG1->GCR1 & 0xFFFFFFFFU) | (0x1 << 24); //Enable SPI

spiREG1->INT0 = (0x1 << 16); //SPI_DMAREQ; Enable DMA REQ only after setting the SPIEN bit to 1.

// spiREG1->DAT1 = 0x00;

while( SPI1_BTCFlag == 0 ){ //DMA block complete interrupt

}

/* USER CODE END */

return 0;

}

/* USER CODE BEGIN (4) */

void dmaGroupANotification(dmaInterrupt_t inttype, uint32 channel)

{

if (inttype == HBC) {

SPI1_HBCFlag = 1;

}

else if (inttype == BTC){

SPI1_BTCFlag = 1;

}

}

void dmaConfigCtrlTxPacket(uint32 sadd, uint32 dadd, uint16 ElmntCnt, uint16 FrameCnt)

{

g_dmaCTRLPKT_TX.SADD = sadd; /* source address */

g_dmaCTRLPKT_TX.DADD = dadd; /* destination address */

g_dmaCTRLPKT_TX.CHCTRL = 0; /* channel control */

g_dmaCTRLPKT_TX.FRCNT = FrameCnt; /* frame count */

g_dmaCTRLPKT_TX.ELCNT = ElmntCnt; /* element count */

g_dmaCTRLPKT_TX.ELDOFFSET = 0; /* element destination offset */

g_dmaCTRLPKT_TX.ELSOFFSET = 0; /* element destination offset */

g_dmaCTRLPKT_TX.FRDOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT_TX.FRSOFFSET = 0; /* frame destination offset */

g_dmaCTRLPKT_TX.PORTASGN = 4; /* port b */

g_dmaCTRLPKT_TX.RDSIZE = ACCESS_16_BIT; /* read size */

g_dmaCTRLPKT_TX.WRSIZE = ACCESS_16_BIT; /* write size */

g_dmaCTRLPKT_TX.TTYPE = FRAME_TRANSFER; /* transfer type */

g_dmaCTRLPKT_TX.ADDMODERD = ADDR_INC1; /* address mode read */

g_dmaCTRLPKT_TX.ADDMODEWR = ADDR_FIXED; /* address mode write */

g_dmaCTRLPKT_TX.AUTOINIT = AUTOINIT_ON; /* autoinit */

}

/* USER CODE END */

Please advise,

Thanks,

Ofir