Other Parts Discussed in Thread: AM2634, AM2632

Tool/software:

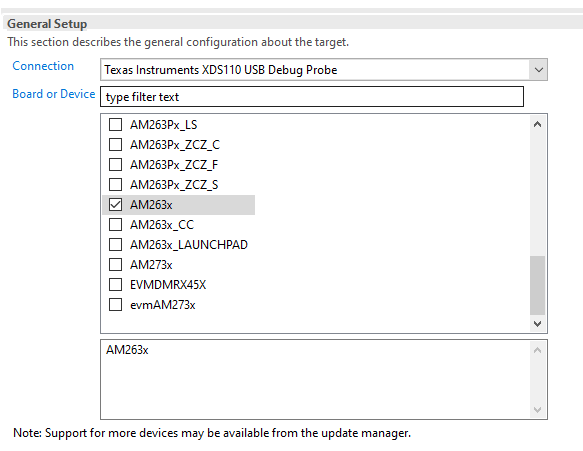

Background:

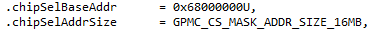

We are plan to use MT29F4G08ADAFAH4 nand with GPMC. And the program is based on sdk_am263x_10_02_00_13.

There is gpmc_v0 driver module and the file name is gpmc_nandlike_v0.c .The file path is source/drivers/gpmc/v0/

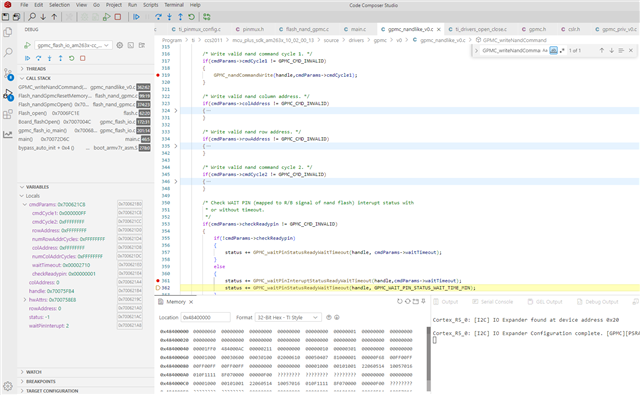

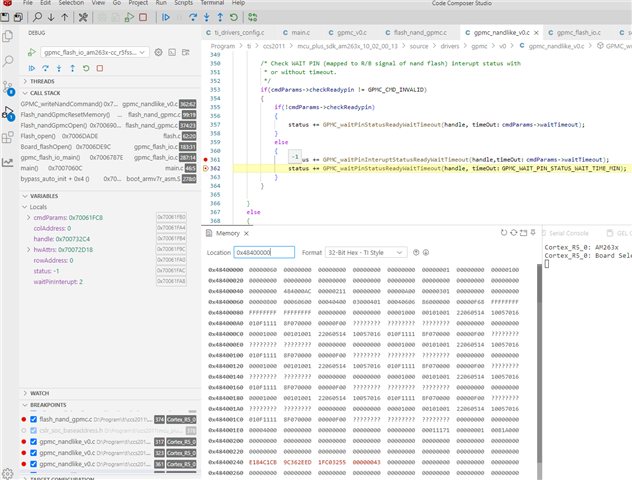

Now we are stuck in the function of GPMC_writeNandCommand() which called by Flash_nandGpmcResetMemory() in flash_nand_gpmc.c

Question

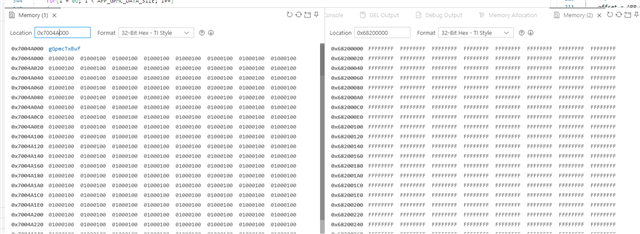

In function GPMC_writeNandCommand(), the GPMC_waitPinInteruptStatusReadyWaitTimeout() always return -1 after calling GPMC_nandCommandWrite(handle,cmdParams->cmdCycle1);

I think that we can't reset memory successfully.

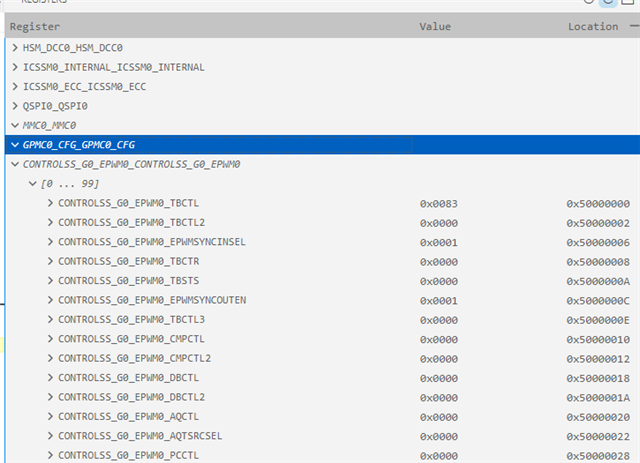

You can see picture for more information.

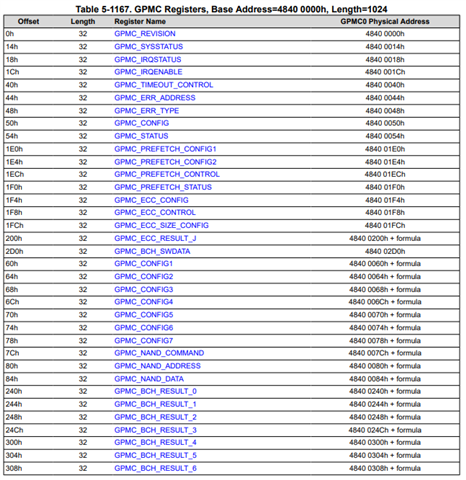

Command Register : 0x4840007C and Address Register : 0x48400080

The cmdParams->cmdCycle1 is 0xFF