Part Number: AM2432

Tool/software:

Hi,

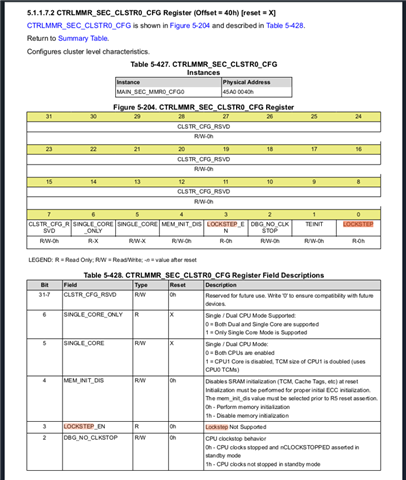

We discovered that if we run single-core application on am2432 , core 0 gets whole TCM memory (128 kbytes) or core 0, while second core is not available (impossible to connect with debugger).

e2e contains contradictive information

a) on the one hand

says that

:

1. After Power On Reset, the R5F0 core is initially in Lockstep mode.

2. If your app image contains code for both cores, then our SBL configures it into Dual Core mode.

3. If your app image contains code only for a single core, then it is configured to Lockstep mode.

b) On other hand "Device does not support lockstep mode and that statement wasn't accurate when it was made"

The question are

1. what happens when am2432 boots with single R5 core application?

2. why second core is not available to debugger?

3. is it normal and by design that core 0 gets all TCM without any configuration efforts ?

4. should we expect some side effects like impact to perfromance.

Thanks

Rasty