Part Number: MSPM0G3519

Other Parts Discussed in Thread: DRV3901-Q1,

Tool/software:

Hello,

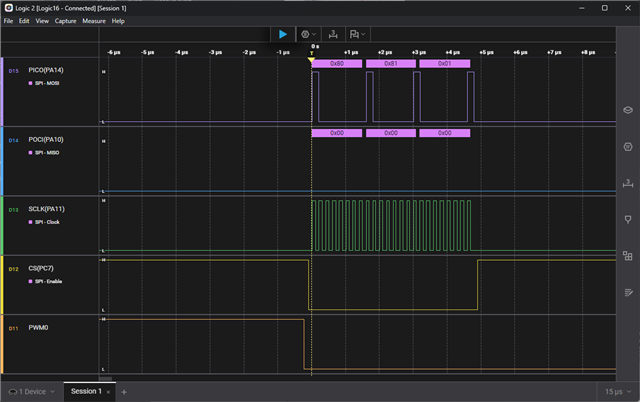

I need to communicate to DRV3901-Q1 devices which require 24 bit frames. What would be the approaches to implement this?

- Manual CS control

- or using PACKEN is possible

I would line to use DMA and not sure if manual CS is possible with DMA.

Any suggestion/advice would be helpful.

Regards,

Eugene