Part Number: MSPM0G1507

Other Parts Discussed in Thread: MSPM0G3507

Hi expets,

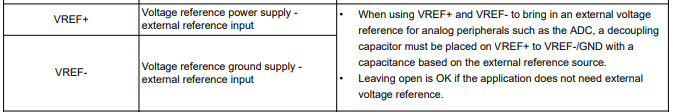

Q1: When using the VREF+/- pins internally, do it still need to connect a decoupling capacitor (CVREF)?

According to the annotation (3) in the datasheet "7.15.2 Electrical Characteristics," a connection is necessary.

However, in the MSPM0 G-Series MCUs Hardware Development Guide (Rev. C) "Table 1-1. MSPM0G Hardware Design Checklist," it is stated that open is acceptable.

Which one is correct?

Q2: When using the VREF+/- pins as VREF, are the internal pull-up/down registers not connected?

I forcefully configured it with the code below, but there was no change in the value.

Background: The customer has created a prototype board using G1507. They are using a modified program based on the sample project "adc12_monitor_supply_lp_mspm0g3507_nortos_ticlang." They are monitoring V3.3, and while the value is stable on the EVM, it is not stable on the prototype board (The 3.3V power supply itself is stable, but MEM0 is unstable). The difference is that VREF+/- is left open. Ideally, I would like to resolve this without using external VCREF.

Best regards,

O.H