Part Number: AM2432

HI TI Team,

We are going to boot up the AM2432xxxxALV using the IS25WX064-JHLE part as a FLASH memory,

due to few resone we are not able to test the boot up processes before the design release.

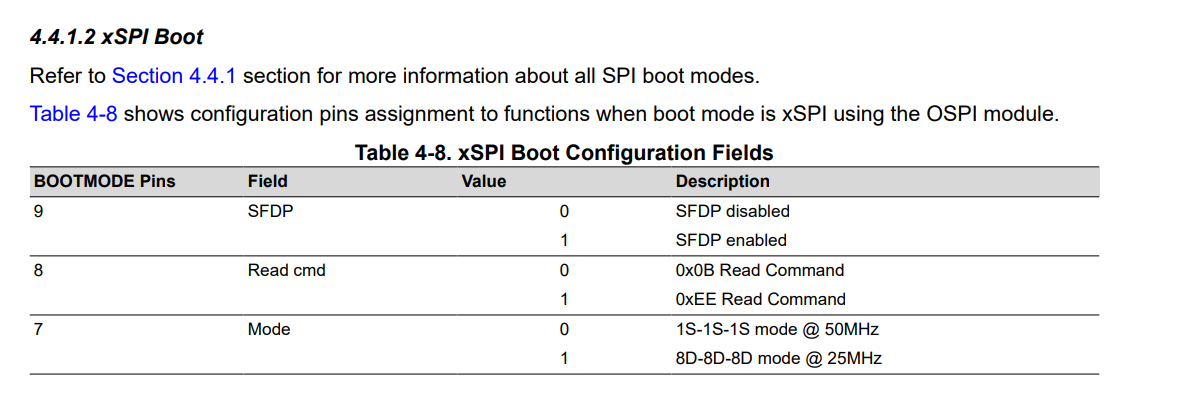

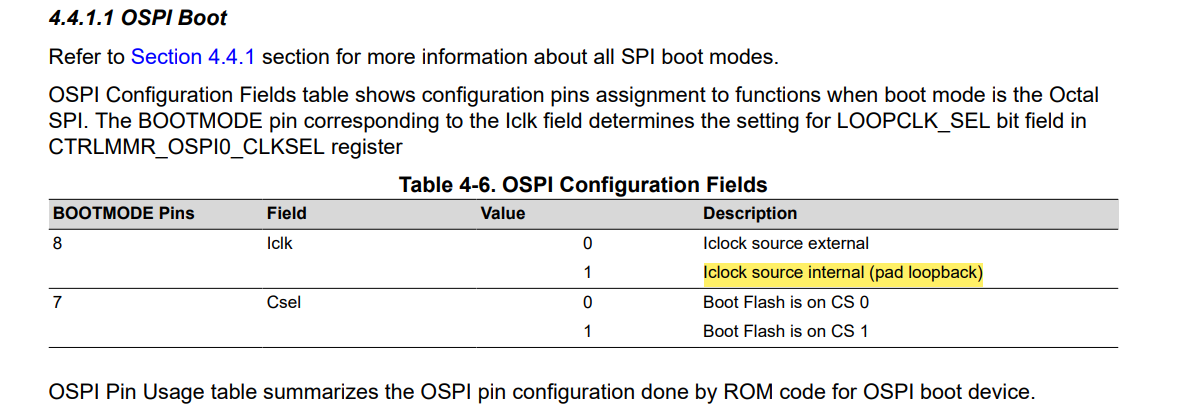

It whould be great if you kindly help us me and check the datasheet of IS25WX064-JHLE and let us know this memory will allow boot of AM2432xxxxALV in OSPI boot mode or xSPI boot mode.

Attached datasheet of memory IS25WX064-JHLE.pdf for your reference.

-

Best Regards,

Vaibhav