I am having problems reading reliably over SMBus using the Utils.

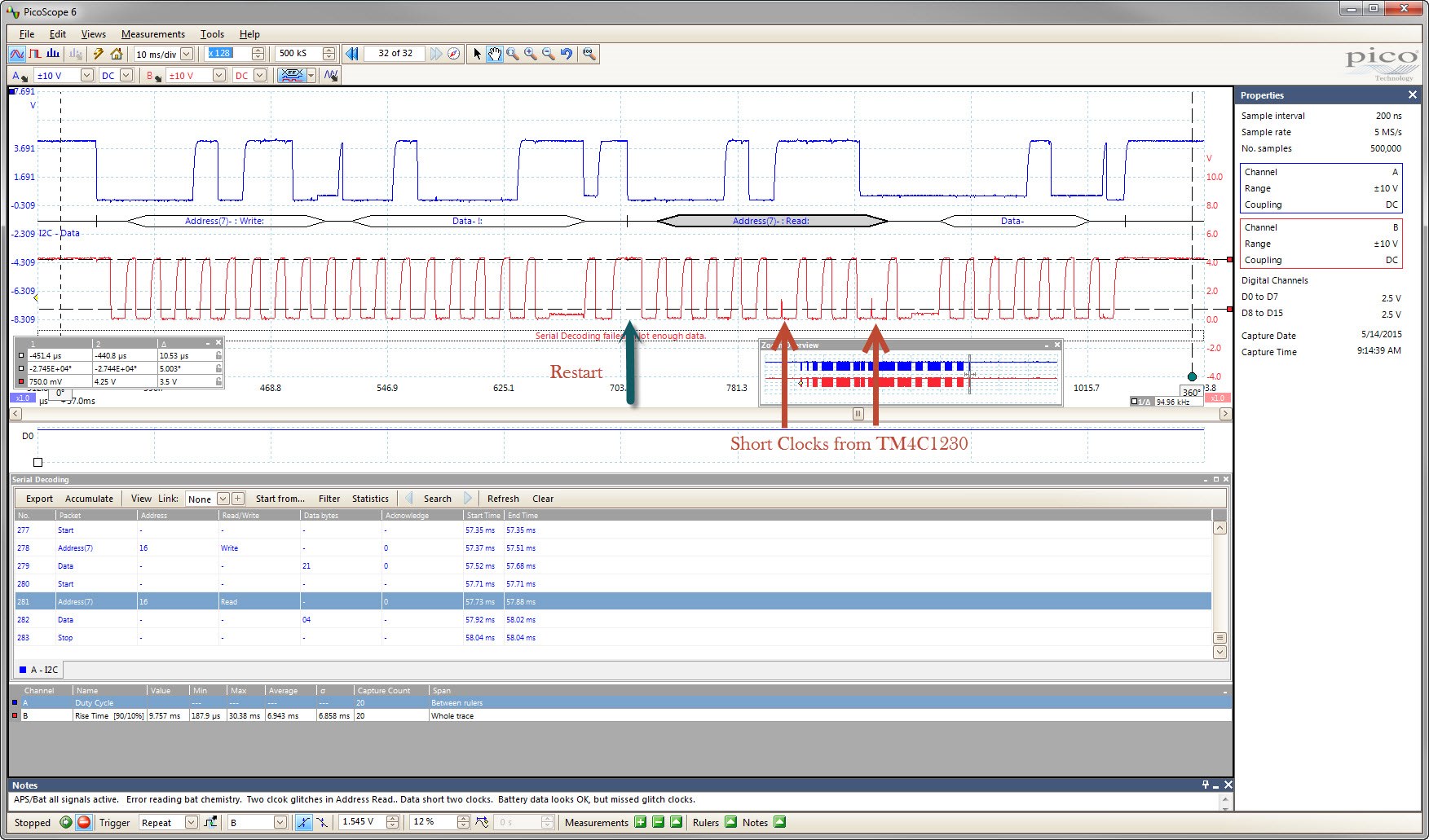

I have tracked down one type of error as an apparent glitch by the TM4C1230 sending out a short clock pulse in the middle of shifting out from the TI Master. Byte address being sent should be 17x to be a read. If the glitches are counted as valid pulses, the address would be 17. The clock before the next glitch would be where the ACK would come (but the slave lost sync by rejecting the glitch, so it didn't pull data low to ack.

If the glitches were not supposed to be clock pulses, the transmitter stopped clocking too early - there are only 16 full scale pulses in the Read Address / Read Data sequence when there need to be 18. But there are two short pulses. This leads me to believe that these pulses are not noise, but are abbreviated clocks.

I don't see any way that the software could shorten the clock pulses.

Any ideas?