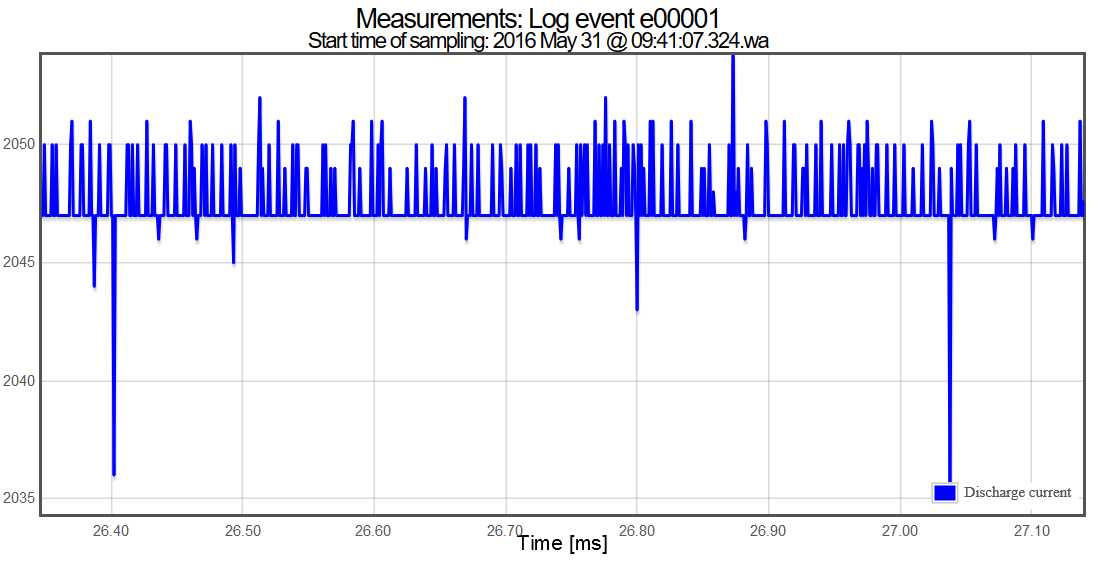

At the Ain2 A/D input, noise spikes are observed at fixed DC input. The device is TM4C129ENCPDT silicon rev 3. See this recording:

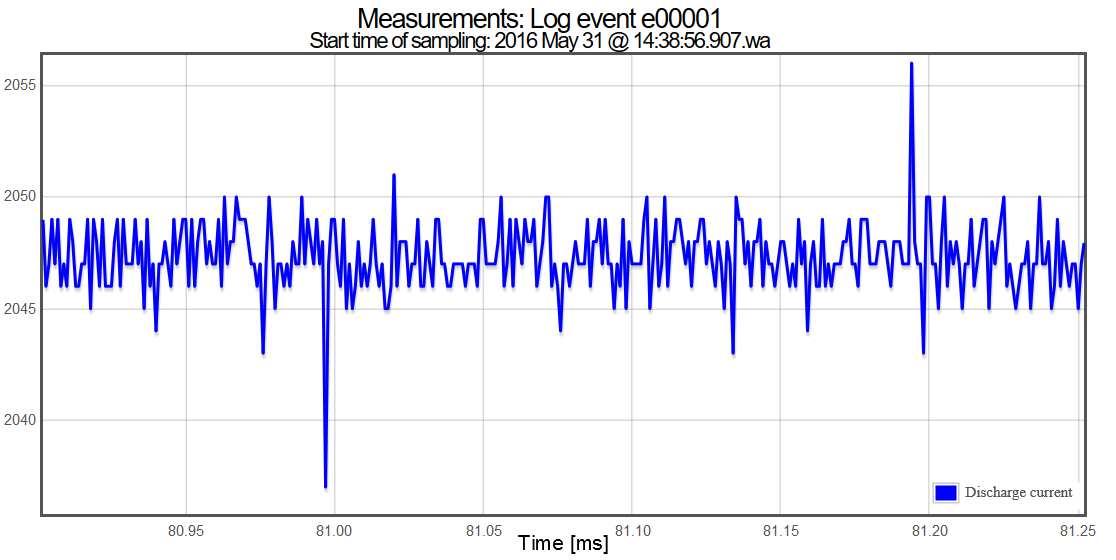

When zooming it looks like this:

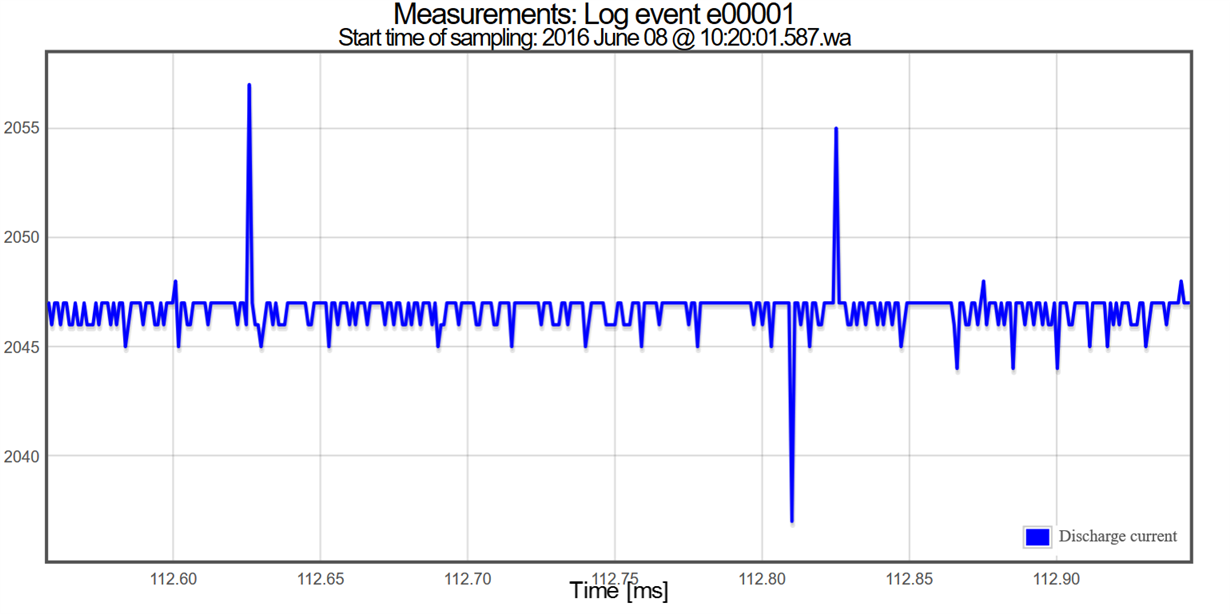

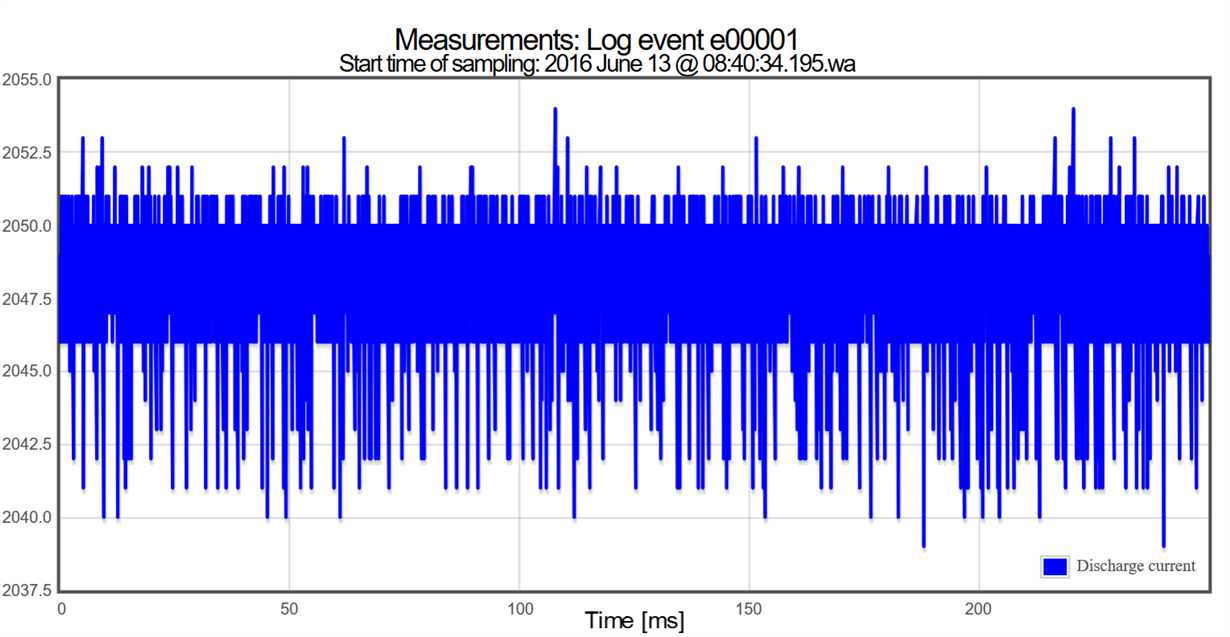

The input is a resistive voltage division from the separate power supply (3.3V) for the analog GNDA and VREF+/VDDA. The input is filteret by a 100nF capacitor to GNDA and all components are placed few mm from the device pins. VREFA+ and VDDA pins are tied together. The actual test is for full speed 2 MSPS, but the same result shows for 500 KSPS. I have tried 64 clock Sample/hold but it does not affect these pictures. The errata tells about spikes at the Ain0, but not at the other inputs. The PCB is well designed using 4 layers. The processor is running RTOS and Ethernet traffic at the same time. Configuration is 'ADC_TRIGGER_ALWAYS'.

Any ideas if this is an expected behavior or how to make better performance in terms of noise ?