TM4C1294i3NCPDT:

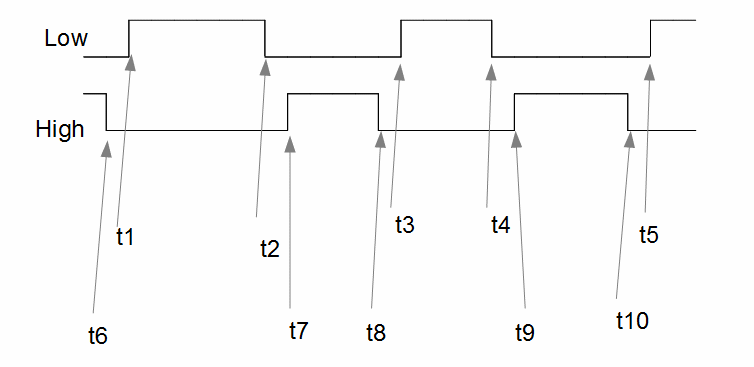

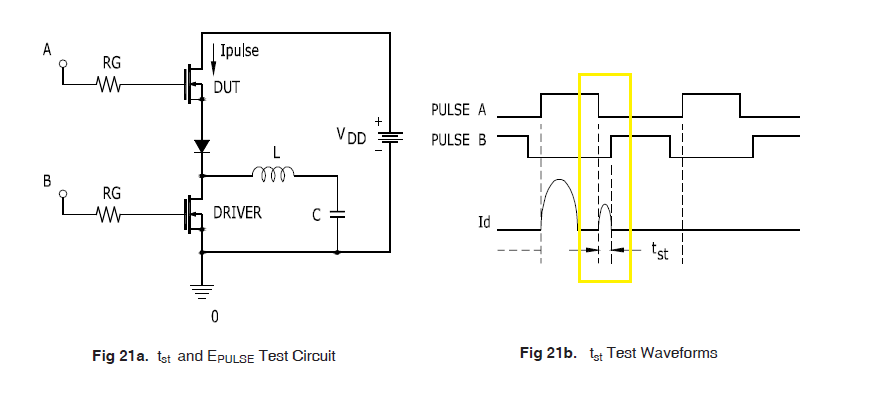

There is a datasheet stated limitation pwmA pulse width must be kept higher than PWMnDBRISE pulse width value at all times.

Ok by how many PWM clocks must pwmA pulse width remain above PWMnDBRISE pulse width when PWM duty cycle is near 100%?

The number of PWM clocks required for setup and propagation delay of signals entering dead band generators is critical when PWMnDBCTRL are being toggled in the duty cycle of pwmA. There are no timing values in table 27.62 to indicate PWMnDBCTRL enable time or PWMnDBRISE being valid PWM clocks when PWMnDBCTRL is toggled at a frequency 8-80 KHz and in this case 80us periods 12.5Khz. Any highly efficient inverter might benefit in light of such disclosure.

There is definitely an undisclosed minimum number PWM clocks required to keep pwmA above PWMnDBRISE. Guessing PWM clocks required can lead to random crashing the PWM generator and poor 1/2 bridge efficiency engineers guess clocks wrong.