Other Parts Discussed in Thread: LM94022, INA240

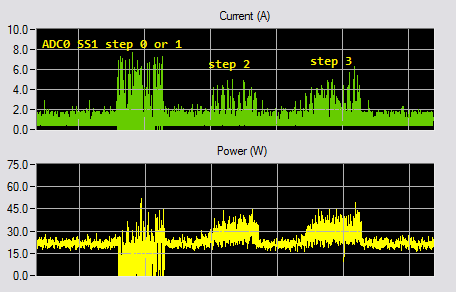

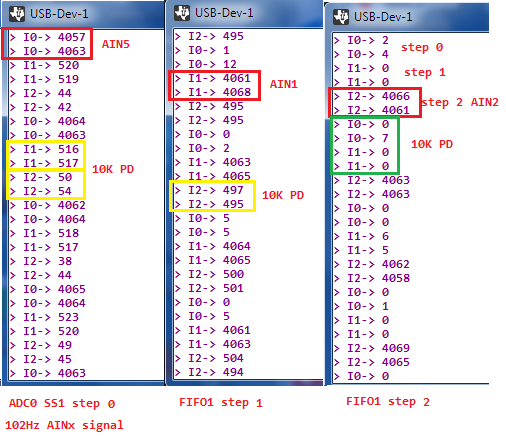

After more KISS testing of ADC0 SS1 step 0 or 1 FIFO1 data seems to produce differential signals in scope widget. However step 2 or 3 if step 0 is disabled, step 1 seems to produce the same results shown below. The digital value reading of step 1 traverses far more negative than the scope widget can show.

How can input differential mode be set on a channel pair, e.g steps 0 or 1 when it was not configured via software? In the code below the same differential output results for step 0 or 1 if the FIFO is pre triggered to render the results of next step. Does it not appear a differential exists in the same signal be placed on AIN5, AIN2, AIN1? This is driving me crazy since it does not add up to being typical behavior of matched channel Rs impedance. What would cause the AIN channel to allow input signal below the others? It would seem this issues can also lead to unrestrained VREFN saturation.

//MAP_ADCSequenceStepConfigure(ADC0_BASE, 1, 0, PIN_IPHASEA); MAP_ADCSequenceStepConfigure(ADC0_BASE, 1, 1, PIN_IPHASEA); // AIN5 MAP_ADCSequenceStepConfigure(ADC0_BASE, 1, 2, PIN_IPHASEB); // AIN1 MAP_ADCSequenceStepConfigure(ADC0_BASE, 1, 3, PIN_IPHASEC | ADC_CTL_END | ADC_CTL_IE); // AIN2