The issue we encounter seems related to https://e2e.ti.com/support/microcontrollers/hercules/f/312/t/518177.

There is no entry in the errata sheet for this issue in rev B. Are you planning to update the errata sheet regarding this issue?

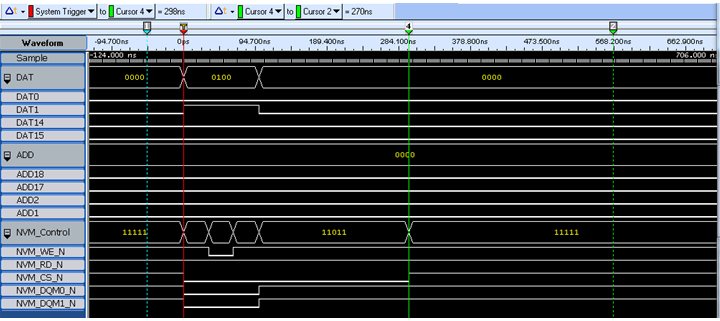

We observed that the CS duration for an access to an asynchronous memory device (connected to CS2) is too long (See screenshot below). The External Bus is running with 30 MHz and all Access Phases are configured to 0 which we expected would result in an access that takes three external clocks.

Is there a possibility to reduce the CS duration or did we miss something in the configuration? There is no external Wait signal used for the NVRAM access.

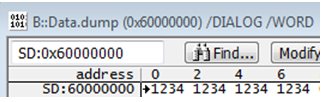

Also when we write 16 bits – 0x1234 - at address 0x6000 0000, we read with the debugger that 64 bits have been written (4x16 bits). I attached a screenshot of a read access. F

Screenshot - EMIF configuration:

Screenshot - Dump at address 0x6000 0000

Screenshot - Write access to NVRAM:

Screenshot - Read access to NVRAM: