Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

I'm working through the CLB example 1 in "SPRUIR8A–September 2019–Revised April 2020".

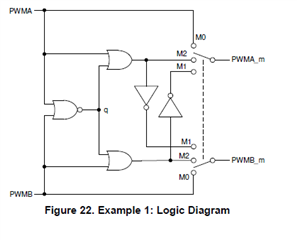

Figure 22 below shows the logic diagram implemented in sysconfig using equations 1,2 and 3 below.

I understand how the signals are configured via the muxes in CCS (C code) example project (clb_ex1_combinatorial_logic).

However, the application note does not mention the process of going from the logic diagram to the implemented equations in SYSCONFIG.

Can anyone provide some guidance?

Thanks for your help

Equations in Sysconfig:

- eq1:= (!i0 & !i1 & i2) | (i0 & !i1 & !(i3 & !(i2 & i3))) | (!i0 & i1 & i2 & !(i2 & i3))

- eq2:= (!i0 & !i1 & i3) | (i0 & !i1 & !(i2 & !(i2 & i3))) | (!i0 & i1 & i3 & !(i2 & i3))

- eq3:= i3

Example 1 Logic diagram.