Other Parts Discussed in Thread: TMDSDOCK28335, CCSTUDIO

Hello,

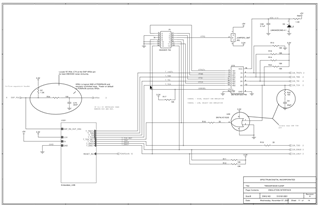

I have two different development boards based on the same DSC and I would like to know what should be taken into account (if it is possible to do) to program the processor in eZdsp TMS320F28335 externally using the programmer included in TMDSDOCK28335 docking Station baseboard JTAG interface which has a XDS100v2 probe. I connected both JTAG headers and tried to test the connection which says that fails with the following message:

This error is generated by TI's USCIF driver or utilities.

The value is '-151' (0xffffff69).

The title is 'SC_ERR_FTDI_OPEN'.

The explanation is:

One of the FTDI driver functions used during the connect

returned bad status or an error. The cause may be one or

more of: no XDS100 is plugged in, invalid XDS100 serial number,

blank XDS100 EEPROM, missing FTDI drivers, faulty USB cable.

Use the xds100serial command-line utility in the 'common/uscif'

folder to verify the XDS100 can be located.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

I have already checked the schematic for both boards and have been searching throughout the forum without finding any mention to this so I may have missing some particular configuration. I hope someone can help me.

Thank you very much and best regards,

Claus