Other Parts Discussed in Thread: C2000WARE

Hi.

I used Application Note https://www.ti.com/lit/sprabv4 for SCI Boot.

Flash Kernel took from ~\C2000Ware_4_00_00_00\device_support\f2837xs\examples\cpu1\F2837xS_sci_flash_kernel\cpu01\

In the file "F2837xS_sci_flash_kernel.c" I replaced the line:

EntryAddr = SCI_GetFunction(SCI_BOOT_ALTERNATE);

on the:

EntryAddr = SCI_GetFunction(SCI_BOOT);

Because I have a 100 pin microcontroller.

GPIO72,84 is (0,1)

The application program is very simple - LED blinking.

Launched:

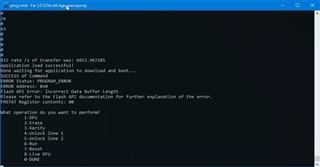

> serial_flash_programmer.exe -d f2837xS -k F2837xS_sci_flash_kernel.txt -a can_485_testBoot.txt -p COM3 -b 9600 -v

Result:

I chose 1-DFU and got the result:

What am I doing wrong?

Thanks.