- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

We have two different revision boards of a design with no changes in the dsp section except for the oscillator. The old board with a 20 MHz oscillator boots just fine after a power reset but the new board with the 30 MHz oscillator does not. Are there any additional settings or changes that we need to make except for the divide ratios in the software to be able to boot the new board or could there be any other issues. The RAM load works just fine on both revisions.

Fred,

Can you comment on the PLLCR setting you were using as well as the modified ones for the 30MHz implementation. Register is at memory address 0x7021, but if you are using our header files, you should just be able to search for PLLCR in your C code.

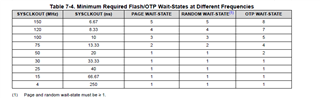

Depending on this we may need to modify the flash WS(WaitStates) if the system clock has increased vs the previous implementation.

Best,

Matthew

For the 30 MHz Version we use the following settings

#define DSP28_DIVSEL 2 // Enable /2 for SYSCLKOUT

#define DSP28_PLLCR 7

we also tried the ones below but no change

#define DSP28_DIVSEL 0 // Enable /4 for SYSCLKOUT

#define DSP28_PLLCR 6

and

#define DSP28_PLLCR 0 // PLL is bypassed in this mode

for the 20 MHz version we use

#define DSP28_PLLCR 10

Fred,

Thanks, so the Flash WS should be OK, moving from 100MHz(with the 20MHz X-tal) to 105MHz(with the 30MHz) both need WS=3 so this would not need to change.

Can you confirm if you are using the InitPLL() function in SysCtrl.c to set up the PLL? This is more for me to confirm the order of operations here.

Any device behaviors that you see with the 30MHz X-tal, i.e. see XRSn pulsing or any indications on where the code may have gotten to in the boot flow?

void

InitPll(Uint16 val, Uint16 divsel)

{

//

// Make sure the PLL is not running in limp mode

//

if (SysCtrlRegs.PLLSTS.bit.MCLKSTS != 0)

{

//

// Missing external clock has been detected

// Replace this line with a call to an appropriate

// SystemShutdown(); function.

//

asm(" ESTOP0");

}

//

// DIVSEL MUST be 0 before PLLCR can be changed from

// 0x0000. It is set to 0 by an external reset XRSn

// This puts us in 1/4

//

if (SysCtrlRegs.PLLSTS.bit.DIVSEL != 0)

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 0;

EDIS;

}

//

// Change the PLLCR

//

if (SysCtrlRegs.PLLCR.bit.DIV != val)

{

EALLOW;

//

// Before setting PLLCR turn off missing clock detect logic

//

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1;

SysCtrlRegs.PLLCR.bit.DIV = val;

EDIS;

//

// Optional: Wait for PLL to lock.

// During this time the CPU will switch to OSCCLK/2 until

// the PLL is stable. Once the PLL is stable the CPU will

// switch to the new PLL value.

//

// This time-to-lock is monitored by a PLL lock counter.

//

// Code is not required to sit and wait for the PLL to lock.

// However, if the code does anything that is timing critical,

// and requires the correct clock be locked, then it is best to

// wait until this switching has completed.

//

//

// Wait for the PLL lock bit to be set.

//

//

// The watchdog should be disabled before this loop, or fed within

// the loop via ServiceDog().

//

//

// Uncomment to disable the watchdog

//

DisableDog();

while(SysCtrlRegs.PLLSTS.bit.PLLLOCKS != 1)

{

//

// Uncomment to service the watchdog

//

//ServiceDog();

}

EALLOW;

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 0;

EDIS;

}

//

// If switching to 1/2

//

if((divsel == 1)||(divsel == 2))

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = divsel;

EDIS;

}

//

// NOTE: ONLY USE THIS SETTING IF PLL IS BYPASSED (I.E. PLLCR = 0) OR OFF

// If switching to 1/1

// * First go to 1/2 and let the power settle

// The time required will depend on the system, this is only an example

// * Then switch to 1/1

//

if(divsel == 3)

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 2;

DELAY_US(50L);

SysCtrlRegs.PLLSTS.bit.DIVSEL = 3;

EDIS;

}

}This should be all your code and we can run the 30 MHz code and flash and start on the old board:

void InitPll(Uint16 val, Uint16 divsel)

{

// Make sure the PLL is not running in limp mode

if (SysCtrlRegs.PLLSTS.bit.MCLKSTS != 0)

{

// Missing external clock has been detected

// Replace this line with a call to an appropriate

// SystemShutdown(); function.

// asm(" ESTOP0");

}

// DIVSEL MUST be 0 before PLLCR can be changed from

// 0x0000. It is set to 0 by an external reset XRSn

// This puts us in 1/4

if (SysCtrlRegs.PLLSTS.bit.DIVSEL != 0)

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 0;

EDIS;

}

// Change the PLLCR

if (SysCtrlRegs.PLLCR.bit.DIV != val)

{

EALLOW;

// Before setting PLLCR turn off missing clock detect logic

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1;

SysCtrlRegs.PLLCR.bit.DIV = val;

EDIS;

// Optional: Wait for PLL to lock.

// During this time the CPU will switch to OSCCLK/2 until

// the PLL is stable. Once the PLL is stable the CPU will

// switch to the new PLL value.

//

// This time-to-lock is monitored by a PLL lock counter.

//

// Code is not required to sit and wait for the PLL to lock.

// However, if the code does anything that is timing critical,

// and requires the correct clock be locked, then it is best to

// wait until this switching has completed.

// Wait for the PLL lock bit to be set.

// The watchdog should be disabled before this loop, or fed within

// the loop via ServiceDog().

// Uncomment to disable the watchdog

DisableDog();

while(SysCtrlRegs.PLLSTS.bit.PLLLOCKS != 1)

{

// Uncomment to service the watchdog

// ServiceDog();

}

EALLOW;

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 0;

EDIS;

}

// If switching to 1/2

if((divsel == 1)||(divsel == 2))

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = divsel;

EDIS;

}

// NOTE: ONLY USE THIS SETTING IF PLL IS BYPASSED (I.E. PLLCR = 0) OR OFF

// If switching to 1/1

// * First go to 1/2 and let the power settle

// The time required will depend on the system, this is only an example

// * Then switch to 1/1

if(divsel == 3)

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 2;

DELAY_US(50L);

SysCtrlRegs.PLLSTS.bit.DIVSEL = 3;

EDIS;

}

}

Fred,

Thanks for this, so that is not an issue either then(PLL setup). I've sent you a message in the forum chat, this may be more efficient there. Will look for your reply there.

Best,

Matthew