- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

In C:\ti\c2000\C2000Ware_DigitalPower_SDK_4_01_00_00\solutions\tidm_02002\f28004x\drivers\source\clllc_hal.c

There is the following code:

//

// setup another slow ADC conversion for ISR3 trigger

//

ADC_setupSOC(CLLLC_ISEC_ADC_MODULE,

CLLLC_ISEC_ADC_SOC_NO_13,

CLLLC_ADC_TRIG_SLOW_SOURCE,

CLLLC_ISEC_ADC_PIN,

CLLLC_ISEC_ADC_ACQPS_SYS_CLKS); //

// setup another slow ADC conversion for ISR3 trigger

//

ADC_setupSOC(CLLLC_VPRIM_ADC_MODULE,

CLLLC_VPRIM_ADC_SOC_NO_13,

CLLLC_ADC_TRIG_SLOW_SOURCE,

CLLLC_VPRIM_ADC_PIN,

CLLLC_VPRIM_ADC_ACQPS_SYS_CLKS); //

// setup another slow ADC conversion for ISR3 trigger

//

ADC_setupSOC(CLLLC_VSEC_ADC_MODULE,

CLLLC_VSEC_ADC_SOC_NO_13,

CLLLC_ADC_TRIG_SLOW_SOURCE,

CLLLC_VSEC_ADC_PIN,

CLLLC_VSEC_ADC_ACQPS_SYS_CLKS);

According to the code and documentation only the third VSEC SOC triggers ISR3 via ADCC2.

1) If that is the case, why are the first (ISEC) and second (VPRIM) SOC13 conversions commented as "ISR3 trigger" please?

2) The first (ISEC) and second (VPRIM) SOC13 conversions seem to be redundant because ISR3 does not read any ADCs as far as I can tell. What are they for please?

Of course, it's quite possible that I've misunderstood how the ADCs work!

Thank you.

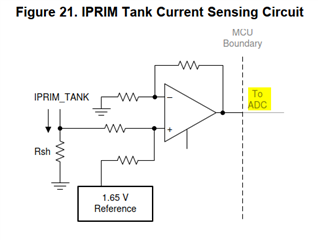

...and a supplementary question 3). I think the following code is redundant because IPRIM_TANK ADC value is not an input to the control system. It is only used as a trip condition in CMPSS, is that correct please?

#define CLLLC_IPRIM_TANK_ADC_MODULE ADCB_BASE #define CLLLC_IPRIM_TANK_ADC_SOC_NO ADC_SOC_NUMBER0 #define CLLLC_IPRIM_TANK_ADC_PIN ADC_CH_ADCIN8 #define CLLLC_IPRIM_TANK_ADC_TRIG_SOURCE CLLLC_ADC_TRIG_FAST_SOURCE #define CLLLC_IPRIM_TANK_ADC_ACQPS_SYS_CLKS 30 #define CLLLC_IPRIM_TANK_ADCRESULTREGBASE ADCBRESULT_BASE #define CLLLC_IPRIM_TANK_ADCREAD ADC_readResult(CLLLC_IPRIM_TANK_ADCRESULTREGBASE, CLLLC_IPRIM_TANK_ADC_SOC_NO)

If so, I think the following figure should say 'To CMPSS' rather than 'To ADC':

Kier,

correct in this design there are two methods of reading the CLLLC_IPRIM, only one is used.

As for the question on why 3 triggers are setup, I don't have the best answer. I can confrim that ADCC2 is causing the interrupt which is caused by an EOC signal which was started using a CPU timer.

The other ADC channels are on ADC's A and B, it appears like the code was setup such that you could switch ADC triggering the interrupt. I suspect this was to make the code more flexible and enable easier porting between devices.

Regards,

Cody