Hi Team,

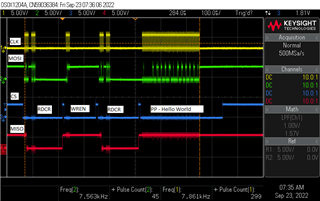

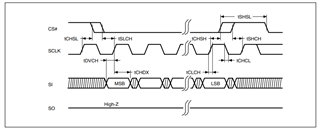

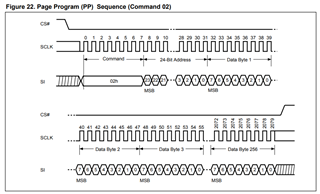

A customer is asking for help on how to use the TMS320F28075 in controlling multiple devices. they want to use the SPI controller in Master mode to make a generic driver where they do the CS using GPIOs. The SPI controller can "control" one CS connection itself but they want to be able to mount multiple devices downstream. the datasheet says in such case that to use GPIO and to code the CS themselves.