Hi everyone,

I have a question regarding the toggle speed of a GPIO pin.

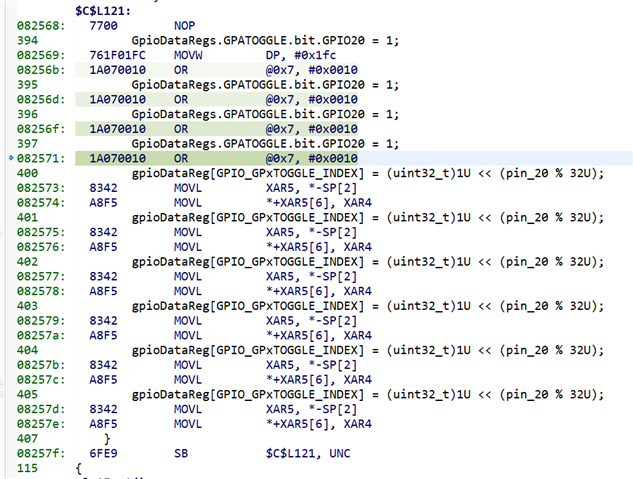

The standard library function e.g. GPIO_togglePin(DEVICE_GPIO_PIN_LED1); has some extra lines of code and so I change the toggle code in the following way:

The first toggle method I checked was with the C code:

GpioDataRegs.GPATOGGLE.bit.GPIO20 = 1;

which gives the ASM code of:

1A070010 OR @0x7, #0x0010

The second toggle method I checked was with the C code:

gpioDataReg[GPIO_GPxTOGGLE_INDEX] = (uint32_t)1U << (pin_20 % 32U);

which gives the ASM code of 2 lines:

082573: 8342 MOVL XAR5, *-SP[2]

082574: A8F5 MOVL *+XAR5[6], XAR4

Question:

the first toggle method (GpioDataRegs.GPATOGGLE.bit.GPIO20 ) takes ~ 58,3 ns to toggle the GPIO pin, but the second method only takes 41,5 ns.

What is the reason for this behavior and how does this fit with the timing CYC of the instructions?

According the data sheet the Bitwise OR should take only 1 CYC. Looking at the disassembly code I expected that running the assembly instruction:

1A070010 OR @0x7, #0x0010

=> total time: 58,3ns

is faster, than running 2 assembly instructions to toggle the pin

082573: 8342 MOVL XAR5, *-SP[2]

082574: A8F5 MOVL *+XAR5[6], XAR4

=> total time: 41,5 ns.

Thanks

Bernhard