Hi Champs,

I am asking for my customer here.

Please help to understand the frequency division setting basis of the ADC clock as below figure? How to choose the frequency division of ADC clock? What is the purpose of setting different ADC clocks?

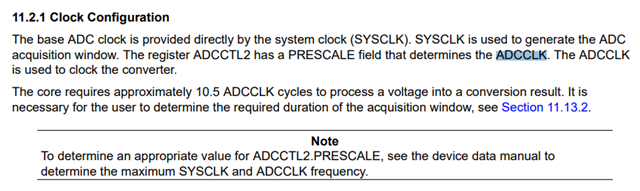

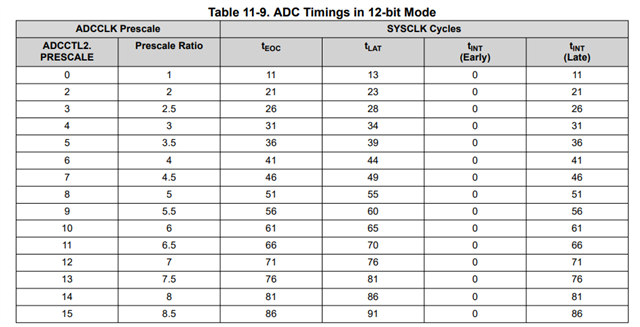

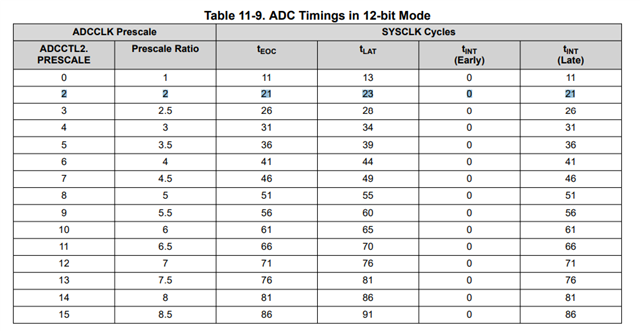

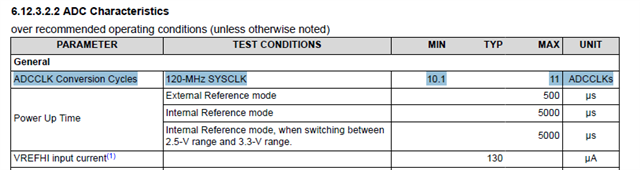

The ADC clock is related to ADC Timing. When the ADC Clock is smaller, the conversion time is longer, so the sampling rate is slower for Slow ADC. And judge from the below figure,

So when the ADCCTL2. PRESCALE = 0, Prescale Ratio = 1, ADC Clock = Sysclk =120MHz >> 60MHz, the ADC conversion time Min is 11ADCCLKS, Right?

But we don't know the significance of setting ADC frequency division? Or what kind of ADC frequency division is applied in the application scenario. Could you give me an example to help understand.

Because from the ADC conversion time, The bigger the ADC Clock, the better, the faster the ADC sampling rate, the better the sampling results and real-time performance. Please help to understand the frequency division setting basis of the ADC clock? Thanks a lot!