Hi BU experts,

Customer asks me some questions, and need your help:

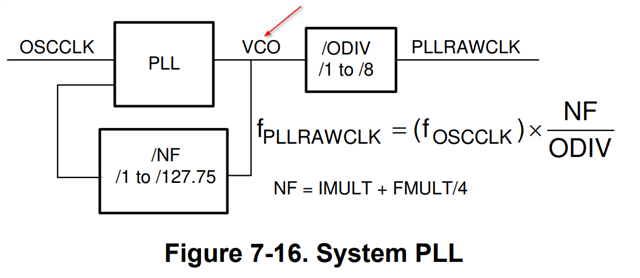

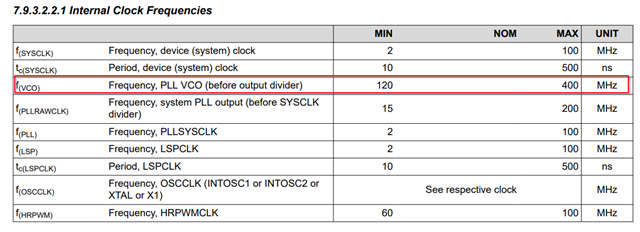

1). If the VCOCLK in the PLL circuit does not meet the spec requirement shown in the datasheet, what will happen? According to customer's configuration, the f(VCO) would be 100M. They want to know the risk of this configuration.

2). If f(VCO) < 120MHz, may the PLL be bypassed by device itself automatically, just like Missing Clock Detection mechanism, and application not know?

Regards,

Will