Hi Team,

There's an issue from the customer need your help:

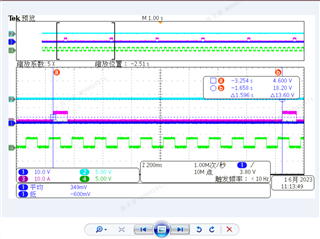

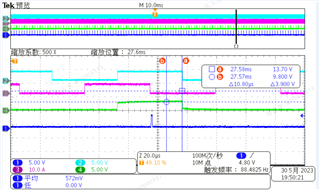

the phase of the input quadrature signal QA is ahead of the phase of QB by 90°, and remains unchanged. Why does QEPSTS[QDF] toggling?

The order in the figure is: QB, QA, index signal and index flag (the index flag is obtained by detecting QFLAG[IEL] using GPIO flipping).

Could you help check this case?

Thanks & Regards,

Ben