Other Parts Discussed in Thread: TMS320F28377D, TMS320F280049

Hi, here I am again with a new question regarding the CMPSS and EPWM interactions. I have solved most of the problems, except for the last (and bigger) one.

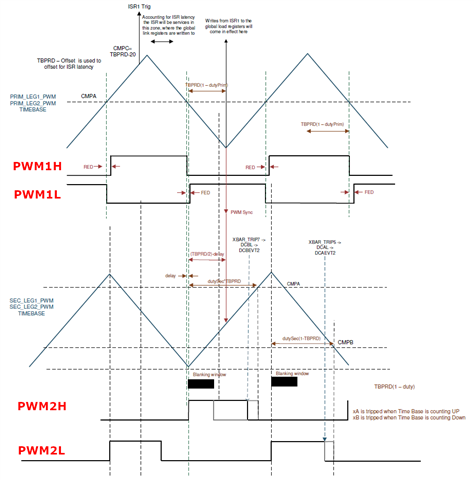

In the TIDM-02002 project, a synchronous rectification scheme has been implemented. Basically a current signal is fed to a comparator, and when it changes sign, the high side or low side PWM is shut down to simulate a diode behavior. When the current goes negative, the high side PWM is shut down; when the current goes positive, the low side PWM is shut down. In the application note (TIDUEG2C) there is a diagram that describes that:

I've added the captions PWMxx for more clarity.

XBAR_TRIP7 is connected to CMPSS2 CTRIPH and it is used to shut down PWM2H, while XBAR_TRIP5 is connected to CMPSS2 CTRIPL and it is used to shut down PWM2L. The CTRIPx signals are latched, and in order for this to work it is necessary to reset the latches at two different times within each PWM cycle: CTRIPH has to be reset during the rising PWM edge, and CTRIPL has to be reset during the falling PWM edge. Otherwise one of the two signals would trip immediately (imagine the current as a sinusoidal signal synchronized with the PWM). And this is exactly what I'm seeing when I run the code.

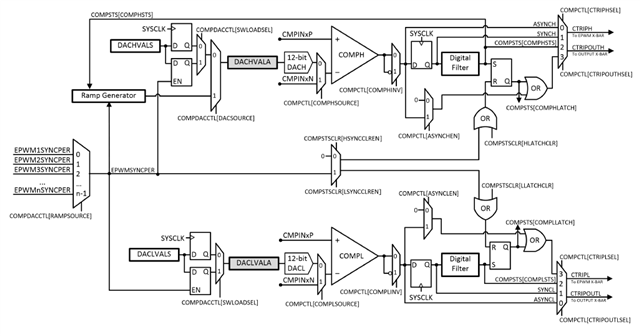

Each CMPSS module is connected to a single EPWMSYNCPER signal, as shown in the technical reference:

Therefore, unless you can generate two EPWMSYNCPER pulses within each PWM cycle (how?), both CTRIPx signals will be reset at the same time. This is exactly what I'm seeing running the code.

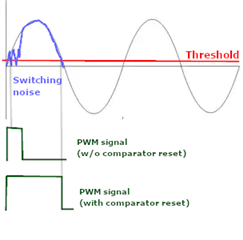

The original TIDM-02002 code was implemented on a TMS320F280049 MCU and had a single feature that is not present in the TMS320F28377D MCU (which I'm currently using), namely the possibility to use the EPWMBLANK signal to reset the CMPSS and to keep it reset for a certain time, in order to filter spurious signals close to the PWM switching. On the first figure you can see the two blanking periods (black rectangles) at the beginning of the PWM2L/PWM2H cycles.

Perhaps is this EPWMBLANK signal that can be generated twice within a cycle? How can I obtain the same result with 377D?

At the moment the only idea I have is to connect the current signal to two different comparators, using the CTRIPH of one of them and the CTRIPL of the other, in order to be able to use two different EPWMSYNCPER signals to reset each of them. But it seems quite a convoluted solution.

Thank you!

L.