Dear TI members,

I am attaching a code of my simulation for PID. I need your help to just explain parts of the code:

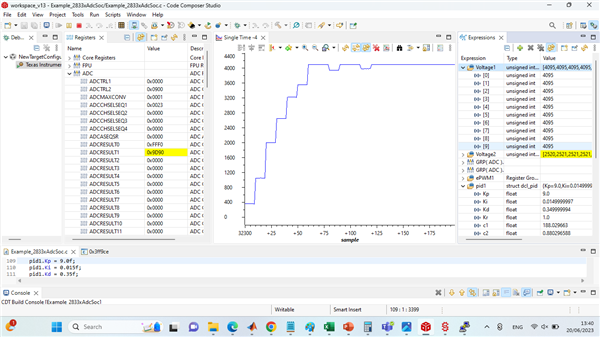

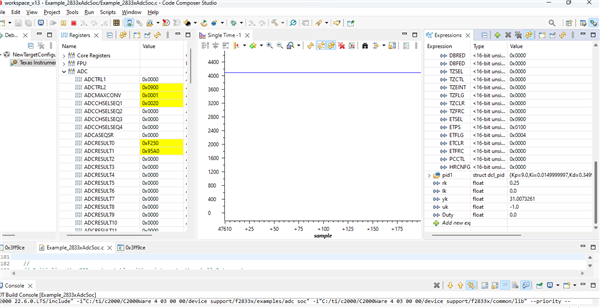

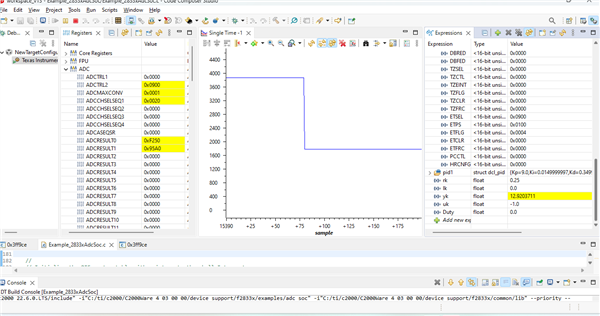

Firstly: If rk =0.25 is set, then yk was achieved with the help of 12 bit ADC values (0-4095) and from the code line 342:

yk = ((float) AdcRegs.ADCRESULT0 - 2048.0f) / 2047.0f;

yk could be between 1 and -1 .........if (float) AdcRegs.ADCRESULT0 between (4095 and 0).

Now, next line 345 : uk = DCL_runPID_C4(&pid1, rk, yk, lk);......for running the PID function. which gives Control effort value u(k).

Question1 : Question is what could be the u(k) value range in numbers??? Please explain this line 345.

Line 348: clampactive = DCL_runClamp_C1(&uk, upperlim, lowerlim); defining the upper and lower limit saturation.

Question 2: Line 350: lk = (clampactive == 0U) ? 1.0f : 0.0f;.... There is no compulsion for choosing either 1 or 0 for clampactive. and can we choose any of them????

For line 353-354:

Duty = (uk / 2.0f + 0.5f) * (float) EPwm1Regs.TBPRD;

EPwm1Regs.CMPA.half.CMPA = (Uint16) Duty;

Question3:

From above line, if u(k) is known from Question 1, then why are we dividing by 2.5 (2.0f+0.5f) and then it multiply with EPwm1Regs.TBPRD ? This Epwm is the one at which we are sampling the ADC at line 286 (EPwm1Regs.TBPRD = 0xFFFF)??? If yes then how this above duty cycle changes if suppose your y(k) changes dues to ADC values? I think I should remove line 309 and then check GPIO0 or GPIO1 to see the change of duty cycle if y(k) changes.

//###########################################################################

//

// FILE: Example_2833xAdcSoc.c

//

// TITLE: ADC Start of Conversion Example

//

//! \addtogroup f2833x_example_list

//! <h1> ADC Start of Conversion (adc_soc)</h1>

//!

//! This ADC example uses ePWM1 to generate a periodic ADC SOC on SEQ1.

//! Two channels are converted, ADCINA3 and ADCINA2.

//!

//! \b Watch \b Variables \n

//! - Voltage1[10] - Last 10 ADCRESULT0 values

//! - Voltage2[10] - Last 10 ADCRESULT1 values

//! - ConversionCount - Current result number 0-9

//! - LoopCount - Idle loop counter

//

//###########################################################################

// $TI Release: $

// $Release Date: $

// $Copyright:

// Copyright (C) 2009-2023 Texas Instruments Incorporated - http://www.ti.com/

//

// Redistribution and use in source and binary forms, with or without

// modification, are permitted provided that the following conditions

// are met:

//

// Redistributions of source code must retain the above copyright

// notice, this list of conditions and the following disclaimer.

//

// Redistributions in binary form must reproduce the above copyright

// notice, this list of conditions and the following disclaimer in the

// documentation and/or other materials provided with the

// distribution.

//

// Neither the name of Texas Instruments Incorporated nor the names of

// its contributors may be used to endorse or promote products derived

// from this software without specific prior written permission.

//

// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

// $

//###########################################################################

//

// Included Files

//

#include "DSP28x_Project.h" // Device Headerfile and Examples Include File

#include "DSP2833x_Device.h"

#include "DSP2833x_Examples.h"

#include "DSP2833x_GlobalPrototypes.h"

#include "DCLF32.h"

//

// Function Prototypes

//

void gpio_select(void);

void Setup_ePWM1(void);

__interrupt void adc_isr(void);

//

// Globals

//

Uint16 LoopCount;

Uint16 ConversionCount;

Uint16 Voltage1[10];

Uint16 Voltage2[10];

//DCL_PID pid1 = PID_DEFAULTS;

//typedef struct dcl_pid pid1;

struct dcl_pid pid1;

//float pid1;

DCL_PID pid1 = PID_DEFAULTS;

float32_t yk;

float32_t lk;

float32_t uk;

//float32_t rk = 0.25; // initial value for control reference

//float32_t lk = 1.0; // control loop not saturated

float32_t rk; // initial value for control reference

float32_t lk; // control loop not saturated

float Duty;

float upperlim = 0.95;

float lowerlim = 0.05;

unsigned int clampactive;

//

// Main

//

void main(void)

{

//DCL_PID pid1 = PID_DEFAULTS;

pid1.Kp = 9.0f;

pid1.Ki = 0.015f;

pid1.Kd = 0.35f;

pid1.Kr = 1.0f;

pid1.c1 = 188.0296600613396f;

pid1.c2 = 0.880296600613396f;

pid1.d2 = 0.0f;

pid1.d3 = 0.0f;

pid1.i10 = 0.0f;

pid1.i14 = 1.0f;

pid1.Umax = 1.0f;

pid1.Umin = -1.0f;

rk = 0.25; // initial value for control reference

lk = 1.0;

//

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

// This example function is found in the DSP2833x_SysCtrl.c file.

//

InitSysCtrl();

EALLOW;

#if (CPU_FRQ_150MHZ) // Default - 150 MHz SYSCLKOUT

//

// HSPCLK = SYSCLKOUT/2*ADC_MODCLK2 = 150/(2*3) = 25.0 MHz

//

#define ADC_MODCLK 0x3

#endif

#if (CPU_FRQ_100MHZ)

//

// HSPCLK = SYSCLKOUT/2*ADC_MODCLK2 = 100/(2*2) = 25.0 MHz

//

#define ADC_MODCLK 0x2

#endif

EDIS;

//

// Define ADCCLK clock frequency ( less than or equal to 25 MHz )

// Assuming InitSysCtrl() has set SYSCLKOUT to 150 MHz

//

EALLOW;

SysCtrlRegs.HISPCP.all = ADC_MODCLK;

EDIS;

//

// Step 2. Initialize GPIO:

// This example function is found in the DSP2833x_Gpio.c file and

// illustrates how to set the GPIO to it's default state.

//

// InitGpio(); // Skipped for this example

//

// Step 3. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

//

DINT;

//

// Initialize the PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the DSP2833x_PieCtrl.c file.

//

InitPieCtrl();

//

// Disable CPU interrupts and clear all CPU interrupt flags:

//

IER = 0x0000;

IFR = 0x0000;

//

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in DSP2833x_DefaultIsr.c.

// This function is found in DSP2833x_PieVect.c.

//

InitPieVectTable();

//

// Interrupts that are used in this example are re-mapped to

// ISR functions found within this file.

//

EALLOW; // This is needed to write to EALLOW protected register

PieVectTable.ADCINT = &adc_isr;

EDIS; // This is needed to disable write to EALLOW protected registers

//* configure ePWM1 */

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

//InitEPwm1Gpio(); // [F2806x_EPwm.c]

gpio_select();

Setup_ePWM1(); // init ePWM1A

//void Setup_ePWM1(void)

//{

//EPwm1Regs.TBCTL.bit.CTRMODE = 3; // freeze TB counter

//EPwm1Regs.TBCTL.bit.PRDLD = 1; // immediate load

//EPwm1Regs.TBCTL.bit.PHSEN = 0; // disable phase loading

//EPwm1Regs.TBCTL.bit.SYNCOSEL = 3; // disable SYNCOUT signal

//EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0; // TBCLK = SYSCLKOUT

//EPwm1Regs.TBCTL.bit.CLKDIV = 0; // clock divider = /1

//EPwm1Regs.TBCTL.bit.FREE_SOFT = 2; // free run on emulation suspend

//EPwm1Regs.TBPRD = 0x2328; // set period for ePWM1 (0x2328 = 10kHz)

//EPwm1Regs.TBPHS.all = 0; // time-base Phase Register

//EPwm1Regs.TBCTR = 0; // time-base Counter Register

//EPwm1Regs.ETSEL.bit.SOCAEN = 1; // enable SOC on A group

//EPwm1Regs.ETSEL.bit.SOCASEL = 1; // select SOC from zero match

//EPwm1Regs.ETPS.bit.SOCAPRD = 1; // generate pulse on 1st event

//EPwm1Regs.CMPCTL.bit.SHDWAMODE = 0; // enable shadow mode

//EPwm1Regs.CMPCTL.bit.LOADAMODE = 2; // reload on CTR=zero

//EPwm1Regs.CMPA.half.CMPA = 0x0080; // set compare A value

//EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // HIGH on CMPA up match

//EPwm1Regs.AQCTLA.bit.ZRO = AQ_CLEAR; // LOW on zero match

//}

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

//

// Step 4. Initialize all the Device Peripherals:

// This function is found in DSP2833x_InitPeripherals.c

//

// InitPeripherals(); // Not required for this example

InitAdc(); // For this example, init the ADC

//

// Step 5. User specific code, enable interrupts:

//

//gpio_select();

//Setup_ePWM1(); // init ePWM1A,ePWM1B

//

// Enable ADCINT in PIE

//

PieCtrlRegs.PIEIER1.bit.INTx6 = 1;

IER |= M_INT1; // Enable CPU Interrupt 1

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

LoopCount = 0;

ConversionCount = 0;

//

// Configure ADC

//

AdcRegs.ADCMAXCONV.all = 0x0001; // Setup 2 conv's on SEQ1

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x3; // Setup ADCINA3 as 1st SEQ1 conv.

AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x2; // Setup ADCINA2 as 2nd SEQ1 conv.

//

// Enable SOCA from ePWM to start SEQ1

//

AdcRegs.ADCTRL2.bit.EPWM_SOCA_SEQ1 = 1;

AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1; // Enable SEQ1 interrupt (every EOS)

//

// Assumes ePWM1 clock is already enabled in InitSysCtrl();

//

EPwm1Regs.ETSEL.bit.SOCAEN = 1; // Enable SOC on A group

EPwm1Regs.ETSEL.bit.SOCASEL = 4; // Select SOC from from CPMA on upcount

EPwm1Regs.ETPS.bit.SOCAPRD = 1; // Generate pulse on 1st event

EPwm1Regs.CMPA.half.CMPA = 0x0080; // Set compare A value

EPwm1Regs.TBPRD = 0xFFFF; // Set period for ePWM1

EPwm1Regs.TBCTL.bit.CTRMODE = 0; // count up and start

//

// Wait for ADC interrupt

//

for(;;)

{

LoopCount++;

}

}

//

void Setup_ePWM1(void)

{

EPwm1Regs.TBCTL.bit.CTRMODE = 3; // freeze TB counter

EPwm1Regs.TBCTL.bit.PRDLD = 1; // immediate load

EPwm1Regs.TBCTL.bit.PHSEN = 0; // disable phase loading

EPwm1Regs.TBCTL.bit.SYNCOSEL = 3; // disable SYNCOUT signal

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0; // TBCLK = SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = 0; // clock divider = /1

EPwm1Regs.TBCTL.bit.FREE_SOFT = 2; // free run on emulation suspend

EPwm1Regs.TBPRD = 0x2328; // set period for ePWM1 (0x2328 = 10kHz)

EPwm1Regs.TBPHS.all = 0; // time-base Phase Register

EPwm1Regs.TBCTR = 0; // time-base Counter Register

EPwm1Regs.ETSEL.bit.SOCAEN = 1; // enable SOC on A group

EPwm1Regs.ETSEL.bit.SOCASEL = 1; // select SOC from zero match

EPwm1Regs.ETPS.bit.SOCAPRD = 1; // generate pulse on 1st event

EPwm1Regs.CMPCTL.bit.SHDWAMODE = 0; // enable shadow mode

EPwm1Regs.CMPCTL.bit.LOADAMODE = 2; // reload on CTR=zero

EPwm1Regs.CMPA.half.CMPA = 0x0080; // set compare A value

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // HIGH on CMPA up match

EPwm1Regs.AQCTLA.bit.ZRO = AQ_CLEAR; // LOW on zero match

}

void gpio_select(void)

{

EALLOW;

GpioCtrlRegs.GPAPUD.bit.GPIO0 = 0; // Enable pullup on GPIO0

GpioCtrlRegs.GPAPUD.bit.GPIO1 = 0; // Enable pullup on GPIO1

GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1; // GPIO0 = PWM1A

GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 1; // GPIO0 = PWM1B

EDIS;

}

// adc_isr -

//

__interrupt void

adc_isr(void)

{

Voltage1[ConversionCount] = AdcRegs.ADCRESULT0 >>4;

Voltage2[ConversionCount] = AdcRegs.ADCRESULT1 >>4;

// read ADC channel

yk = ((float) AdcRegs.ADCRESULT0 - 2048.0f) / 2047.0f;

// run PID controller

uk = DCL_runPID_C4(&pid1, rk, yk, lk);

// external clamp for anti-windup reset

clampactive = DCL_runClamp_C1(&uk, upperlim, lowerlim);

//clampactive = DCL_runClamp_C1(&uk, Umax, Umin);

lk = (clampactive == 0U) ? 1.0f : 0.0f;

// write u(k) to PWM

Duty = (uk / 2.0f + 0.5f) * (float) EPwm1Regs.TBPRD;

EPwm1Regs.CMPA.half.CMPA = (Uint16) Duty;

//

// If 40 conversions have been logged, start over

//

if(ConversionCount == 9)

{

ConversionCount = 0;

}

else

{

ConversionCount++;

}

//

// Reinitialize for next ADC sequence

//

AdcRegs.ADCTRL2.bit.RST_SEQ1 = 1; // Reset SEQ1

AdcRegs.ADCST.bit.INT_SEQ1_CLR = 1; // Clear INT SEQ1 bit

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; // Acknowledge interrupt to PIE

return;

}

//

// End of File

//

Please explain all the questions step by step. Sorry I am new to using DCL PID simulation.

Thanks

Regards

Arsalan