Hi BU,

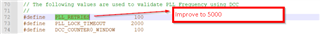

Customer met some F280041 devices' response time too long (in their system booting phase, main MCU needs to receive the F280041's response, if the response time too long, the main MCU will report error to car central controller). They tested the RST pin and crystal pin waveform, and found that after several reset cycle then the crystal oscillator start to oscillation. The reason behind this phenomenon is that in their codes for F280041, not only use the following retry loop to avoid the PLL errata, but also when retry times (100 times) is reach, they will start the watchdog and reset the device.

So the phenomenon means that the F280041 resets itself several times and retried several 100 times to lock the PLL, and then success. But this time is too long for customer's system timing spec.

Customer requests me to answer following questions, please help:

1. what is the truly root cause for the errata- PLL May Not Lock on the First Lock Attempt? Physical root cause and the corresponding function faults to cause this errata.

2. why the device could recover from this errata after resetting itself several times? Can they add the retry times to recover? Or can they decrease the retry times but use reset to recover the device, which can short the total time for recovering, so that can meet their system timing spec.

Thanks & Regards,

Will

Regards,

Will