- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

I am implementing control for phase shifted full bridge converter with TMS320F280041 microcontroller.

Power is controlled with EPWM1-EPWM4 phase shift. EPWM1 and EPWM4 are set in up-down mode and linked (EPWM1 sync out is used as EPWM4 sync in and phase controlled with TBPHS registers). Freq is 100kHz and duty 50%. Phase shift is in range [1; 0,5] (epwm1 lags after epwm4). Control loop frequency is 10kHz

This is working fine for me.

However, I am trying to implement synchronous rectifier control on EPM7 with usage of EPWM1 and EPM4 output OFF and ON events, similar like described with this topic:

https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1158329/tms320f280048-q1-how-to-obtain-sr-waveforms-by-monitoring-other-epwm-channels-on-and-off-edges?tisearch=e2e-sitesearch&keymatch=synchronize%252520rectifier#

I am using T1 event to do that, the idea is:

EPWM1: up-down mode, turn ON at CMPA up, turn OFF on CMPA down

EPWM4: up-down mode, turn ON at CMPA up, turn OFF on CMPA down, with phase shift in relation to EPWM1, CMPB-equal to CMPA is sync out for EPWM7

EPWM7: up-down mode, as default set as EPWM1, but sync in from EPWM4 used as T1 event, so output is controlled with T1 and CMPA events

As I see, that logic of T1 is related to phase shift. When phase shift is greater than 0.75, then my event for controlling EPWM7 output is T1D, below 0.75 this event changes to T1U.

So with that I must change "on the fly" configuration of action qualifier for EPWM7.

The problem is that, when I change this configuration when phase shift is 0.75 (which I do with checking TBPRD and TBPHS registers and their relation), then it looks like that sometimes it is too soon -

action qualifier configuration was changed so it reacts to T1U instead of T1D and this is ruining desired PWM waveform.

Could you help me investigate and understand this issue? I will update this topic with code and images later if needed.

I would like to stay with T1 event approach as I am using digital compare module with CMPSS for protection

Hi Dawid:

Could you clarify this statement:

"CMPB-equal to CMPA is sync out for EPWM7"

There is no configuration to generate a sync out pulse on CMPA==CMPB. Is this what you meant?

Is EPWM7 synchronized with EPWM1? What is the sync in source for EPWM7?

Thank you,

Luke

This is a complex configuration. If you could also send a scope shot of the waveform you're seeing, a diagram or description of the desired waveform, and list all of the settings that are being changed during run-time that would be helpful to resolve this issue.

Hi Luke,

Sorry for late response, I had a problems with posting anything.

"CMPB-equal to CMPA is sync out for EPWM7" it means that CMPB of EPWM4 has the same value as CMPA of EPWM4, and CMPB is sync out source for EPWM7.

Below is my code configuration of relevant settings. Actually descibed configuration changed a little bit: I needed to implement some delay on synchronous rectifier, so it was done with rising edge deadtime on EPWM7A and EPWM8A output.

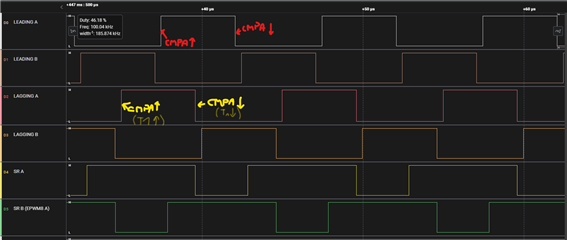

Here is a waveform which I want to achieve - example for MODE 2

And here is my situation with waveforms:

Above phase shift is more than 0.75, so I am switching SR according to my initial configuration of action qualifiers for EPWM7 and EPWM8.

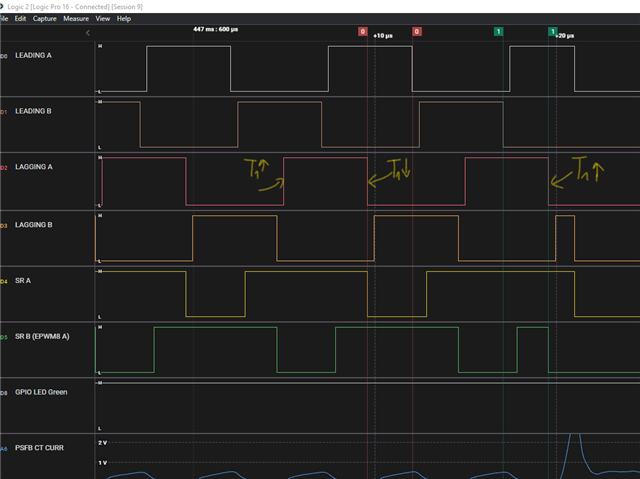

But here is a problem:

Falling edge of EPWM4 becomes my T1 up event before I am able to switch my configuration of action qualifiers.

I tried many configurations of register shadowing or synchronization but I don't understand why it happens in the first place.

Any thoughts?

Best regards

Dawid

/* EPWM1 setting (master): */

EPwm1Regs.TBCTL.bit.CLKDIV = 0;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0;

EPwm1Regs.TBPHS.bit.TBPHS = 0; // set Phase register to zero

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // symmetrical mode

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // master module

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero and Prd

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero and Prd

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm1Regs.AQCTLA.bit.PRD = AQ_NO_ACTION;

EPwm1Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // active Hi complementary

EPwm1Regs.TZCTL.bit.TZA = TZ_NO_CHANGE;

EPwm1Regs.TZCTL.bit.TZB = TZ_NO_CHANGE;

EPwm1Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO;

EPwm1Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm1Regs.ETSEL.bit.SOCAEN = 0;

EPwm1Regs.ETSOCPS.bit.SOCAPRD2 = 1;

EPwm1Regs.outMode = PLX_PWM_OUTPUT_MODE_DUAL;

EPwm1Regs.TBPRD = 500;

EPwm1Regs.TBCTL.bit.CTRMODE = 2;

// activestate is high

EPwm1Regs.DBCTL.bit.POLSEL = 2; // DB_ACTV_HIC

// enable deadtime insertion

EPwm1Regs.DBCTL.bit.OUT_MODE = 3; // DB_FULL_ENABLE

EPwm1Regs.DBCTL.bit.IN_MODE = 0; // DBA_ALL

// TZ settings

EPwm1Regs.TZSEL.bit.CBC1 = 0;

EPwm1Regs.TZSEL.bit.OSHT1 = 0;

EPwm1Regs.TZSEL.bit.CBC2 = 0;

EPwm1Regs.TZSEL.bit.OSHT2 = 0;

EPwm1Regs.TZSEL.bit.CBC3 = 0;

EPwm1Regs.TZSEL.bit.OSHT3 = 0;

// force low when tripped

EPwm1Regs.TZCTL.bit.TZA = 2;

EPwm1Regs.TZCTL.bit.TZB = 2;

// shadowing to allow synchronized disabling of leg

EPwm1Regs.DBCTL2.bit.SHDWDBCTLMODE = 1; // shadow [5:0]of the DBCTL

EPwm1Regs.DBCTL2.bit.LOADDBCTLMODE = 0; // load at zero

EPwm1Regs.AQSFRC.bit.RLDCSF = 0; // load software force on zero

EPwm1Regs.TBCTL.bit.SYNCOSEL = 1;

/* EPWM4 setting (slave): */

EPwm4Regs.TBCTL.bit.CLKDIV = 0;

EPwm4Regs.TBCTL.bit.HSPCLKDIV = 0;

EPwm4Regs.TBPHS.bit.TBPHS = 0; // set Phase register to zero

EPwm4Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // symmetrical mode

EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE; // master module

EPwm4Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero and Prd

EPwm4Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero and Prd

EPwm4Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm4Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm4Regs.AQCTLA.bit.PRD = AQ_NO_ACTION;

EPwm4Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION;

EPwm4Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module

EPwm4Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // active Hi complementary

EPwm4Regs.TZCTL.bit.TZA = TZ_NO_CHANGE;

EPwm4Regs.TZCTL.bit.TZB = TZ_NO_CHANGE;

EPwm4Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO;

EPwm4Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm4Regs.ETSEL.bit.SOCAEN = 0;

EPwm4Regs.ETSOCPS.bit.SOCAPRD2 = 1;

EPwm4Regs.outMode = PLX_PWM_OUTPUT_MODE_DUAL;

EPwm4Regs.TBPRD = 500;

EPwm4Regs.TBCTL.bit.CTRMODE = 2;

// activestate is high

EPwm4Regs.DBCTL.bit.POLSEL = 2; // DB_ACTV_HIC

// enable deadtime insertion

EPwm4Regs.DBCTL.bit.OUT_MODE = 3; // DB_FULL_ENABLE

EPwm4Regs.DBCTL.bit.IN_MODE = 0; // DBA_ALL

// TZ settings

EPwm4Regs.TZSEL.bit.CBC1 = 0;

EPwm4Regs.TZSEL.bit.OSHT1 = 0;

EPwm4Regs.TZSEL.bit.CBC2 = 0;

EPwm4Regs.TZSEL.bit.OSHT2 = 0;

EPwm4Regs.TZSEL.bit.CBC3 = 0;

EPwm4Regs.TZSEL.bit.OSHT3 = 0;

// force low when tripped

EPwm4Regs.TZCTL.bit.TZA = 2;

EPwm4Regs.TZCTL.bit.TZB = 2;

// shadowing to allow synchronized disabling of leg

EPwm4Regs.DBCTL2.bit.SHDWDBCTLMODE = 1; // shadow [5:0]of the DBCTL

EPwm4Regs.DBCTL2.bit.LOADDBCTLMODE = 0; // load at zero

EPwm4Regs.AQSFRC.bit.RLDCSF = 0; // load software force on zero

EPwm4Regs.TBCTL.bit.SYNCOSEL = 0;

EPwm4Regs.TBCTL2.bit.PRDLDSYNC = 1; // load TBPRD at zero and SYNC

EALLOW;

SyncSocRegs.SYNCSELECT.bit.EPWM4SYNCIN = 0;

EDIS;

/* EPWM7 default configuration(SR A on EPWM7A ) */

EPwm7Regs.TBCTL.bit.CLKDIV = 0;

EPwm7Regs.TBCTL.bit.HSPCLKDIV = 0;

EPwm7Regs.TBPHS.bit.TBPHS = 0; // set Phase register to zero

EPwm7Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // symmetrical mode

EPwm7Regs.TBCTL.bit.PHSEN = TB_DISABLE; // master module

EPwm7Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm7Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm7Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm7Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero and Prd

EPwm7Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero and Prd

EPwm7Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm7Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm7Regs.AQCTLA.bit.PRD = AQ_NO_ACTION;

EPwm7Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION;

EPwm7Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module

EPwm7Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // active Hi complementary

EPwm7Regs.TZCTL.bit.TZA = TZ_NO_CHANGE;

EPwm7Regs.TZCTL.bit.TZB = TZ_NO_CHANGE;

EPwm7Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO;

EPwm7Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm7Regs.ETSEL.bit.SOCAEN = 0;

EPwm7Regs.ETSOCPS.bit.SOCAPRD2 = 1;

EPwm7Regs.outMode = PLX_PWM_OUTPUT_MODE_DUAL;

EPwm7Regs.TBPRD = 500;

EPwm7Regs.TBCTL.bit.CTRMODE = 2;

// activestate is high

EPwm7Regs.DBCTL.bit.POLSEL = 2; // DB_ACTV_HIC

// enable deadtime insertion

EPwm7Regs.DBCTL.bit.OUT_MODE = 3; // DB_FULL_ENABLE

EPwm7Regs.DBCTL.bit.IN_MODE = 0; // DBA_ALL

// TZ settings

EPwm7Regs.TZSEL.bit.CBC1 = 0;

EPwm7Regs.TZSEL.bit.OSHT1 = 0;

EPwm7Regs.TZSEL.bit.CBC2 = 0;

EPwm7Regs.TZSEL.bit.OSHT2 = 0;

EPwm7Regs.TZSEL.bit.CBC3 = 0;

EPwm7Regs.TZSEL.bit.OSHT3 = 0;

// force low when tripped

EPwm7Regs.TZCTL.bit.TZA = 2;

EPwm7Regs.TZCTL.bit.TZB = 2;

// shadowing to allow synchronized disabling of leg

EPwm7Regs.DBCTL2.bit.SHDWDBCTLMODE = 1; // shadow [5:0]of the DBCTL

EPwm7Regs.DBCTL2.bit.LOADDBCTLMODE = 0; // load at zero

EPwm7Regs.AQSFRC.bit.RLDCSF = 0; // load software force on zero

EPwm7Regs.TBCTL.bit.SYNCOSEL = 1;

/* EPWM8 default configuration(SR B on EPWM8A ) */

EPwm8Regs.TBCTL.bit.CLKDIV = 0;

EPwm8Regs.TBCTL.bit.HSPCLKDIV = 0;

EPwm8Regs.TBPHS.bit.TBPHS = 0; // set Phase register to zero

EPwm8Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // symmetrical mode

EPwm8Regs.TBCTL.bit.PHSEN = TB_DISABLE; // master module

EPwm8Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm8Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm8Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm8Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero and Prd

EPwm8Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD; // load on CTR=Zero and Prd

EPwm8Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm8Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm8Regs.AQCTLA.bit.PRD = AQ_NO_ACTION;

EPwm8Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION;

EPwm8Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module

EPwm8Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // active Hi complementary

EPwm8Regs.TZCTL.bit.TZA = TZ_NO_CHANGE;

EPwm8Regs.TZCTL.bit.TZB = TZ_NO_CHANGE;

EPwm8Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO;

EPwm8Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;

EPwm8Regs.ETSEL.bit.SOCAEN = 0;

EPwm8Regs.ETSOCPS.bit.SOCAPRD2 = 1;

EPwm8Regs.outMode = PLX_PWM_OUTPUT_MODE_DUAL;

EPwm8Regs.TBPRD = 500;

EPwm8Regs.TBCTL.bit.CTRMODE = 2;

// activestate is high

EPwm8Regs.DBCTL.bit.POLSEL = 2; // DB_ACTV_HIC

// enable deadtime insertion

EPwm8Regs.DBCTL.bit.OUT_MODE = 3; // DB_FULL_ENABLE

EPwm8Regs.DBCTL.bit.IN_MODE = 0; // DBA_ALL

// TZ settings

EPwm8Regs.TZSEL.bit.CBC1 = 0;

EPwm8Regs.TZSEL.bit.OSHT1 = 0;

EPwm8Regs.TZSEL.bit.CBC2 = 0;

EPwm8Regs.TZSEL.bit.OSHT2 = 0;

EPwm8Regs.TZSEL.bit.CBC3 = 0;

EPwm8Regs.TZSEL.bit.OSHT3 = 0;

// force low when tripped

EPwm8Regs.TZCTL.bit.TZA = 2;

EPwm8Regs.TZCTL.bit.TZB = 2;

// shadowing to allow synchronized disabling of leg

EPwm8Regs.DBCTL2.bit.SHDWDBCTLMODE = 1; // shadow [5:0]of the DBCTL

EPwm8Regs.DBCTL2.bit.LOADDBCTLMODE = 0; // load at zero

EPwm8Regs.AQSFRC.bit.RLDCSF = 0; // load software force on zero

EPwm8Regs.TBCTL.bit.SYNCOSEL = 1;

/* Configuring controlling SR with EPWM1 and EPWM4 events

it overwrites some previous settings */

EALLOW;

EPwm7Regs.TBPHS.all = 0x0u;

/*************************************************************/

/* setting for solution on one epwms - config for EPWM7*/

EPwm7Regs.DBCTL.all = 0u; //disable deadband

EPwm7Regs.DBCTL.bit.OUT_MODE = 2; //2 - (Rising Edge Delay in A signal path), 3 - DBM fully active

EPwm4Regs.CMPB.bit.CMPB = EPwm4Regs.CMPA.bit.CMPA;

EPwm4Regs.TBCTL.bit.SYNCOSEL = 2; //syncosel on CMPB

SyncSocRegs.SYNCSELECT.bit.EPWM7SYNCIN = 1; //EPWM4SYNCOUT selected

EPwm7Regs.AQTSRCSEL.bit.T1SEL = 7; //EPWMxSYNCI

EPwm8Regs.DBCTL.all = 0u; //disable deadband

EPwm8Regs.DBCTL.bit.OUT_MODE = 2; //2 - (Rising Edge Delay in A signal path), 3 - DBM fully

EPwm7Regs.TBCTL.bit.SYNCOSEL = 0; //syncosel on CMPB of EPWM4 (EPWM 7 SYNCIN)

EPwm8Regs.AQTSRCSEL.bit.T1SEL = 7; //EPWMxSYNCI

// /* AQCTL setting - shadow registers */

EPwm7Regs.AQCTL.bit.SHDWAQAMODE = 1; //turn on shadow mode for AQCTLA

EPwm7Regs.AQCTL.bit.SHDWAQBMODE = 1; //turn on shadow mode for AQCTLB

EPwm8Regs.AQCTL.bit.SHDWAQAMODE = 1; //turn on shadow mode for AQCTLA

EPwm8Regs.AQCTL.bit.SHDWAQBMODE = 1; //turn on shadow mode for AQCTLB

//

EPwm7Regs.AQCTL.bit.LDAQAMODE = 1; //2-shadow Load on CTR = Zero or CTR = PRD, 0 - on zero

EPwm7Regs.AQCTL.bit.LDAQBMODE = 1; //2-shadow Load on CTR = Zero or CTR = PRD, 0 - on zero

EPwm8Regs.AQCTL.bit.LDAQAMODE = 1; //2-shadow Load on CTR = Zero or CTR = PRD, 1 - on period

EPwm8Regs.AQCTL.bit.LDAQBMODE = 1; //2-shadow Load on CTR = Zero or CTR = PRD, 1 - on period

//

/* when solo EPwmxRegs.AQCTL.bit.LDAQxSYNC = 1; then always logic for A and B is correct */

EPwm7Regs.AQCTL.bit.LDAQASYNC = 1; // 0- Shadow to Active Load of AQCTLB occurs according to LDAQAMODE, 1 - on ldaqamode and sync

EPwm7Regs.AQCTL.bit.LDAQBSYNC = 1; //Shadow to Active Load of AQCTLB occurs according to LDAQAMODE, 1 - on ldaqamode and sync

EPwm8Regs.AQCTL.bit.LDAQASYNC = 1; //Shadow to Active Load of AQCTLB occurs according to LDAQAMODE, 1 - on ldaqamode and sync

EPwm8Regs.AQCTL.bit.LDAQBSYNC = 1; //Shadow to Active Load of AQCTLB occurs according to LDAQAMODE, 1 - on ldaqamode and sync, 2 - only on sync

/* Start with SR disabled */

SynchrRectOnEventsTurnOff();

EDIS;

/* Controlling phase shift for EPWM4 - except this there is also usage of HRPWM */

void EPWM4_setPhase( float aPhase)

{

if((aPhase < 0) || (aPhase >= 1.0))

{

aPhase = 0;

}

uint16_t phase;

uint16_t dir;

if(EPwm4Regs.TBCTL.bit.CTRMODE == TB_COUNT_UPDOWN)

{

// up-down

if (aPhase <= 0.5)

{

// -2 to compensate 2*EPWMCLK delay to synchronize EPWM_master and EPWM_slave

phase = (uint16_t)((float)(EPwm4Regs.TBPRD) * aPhase) -2;

dir = 0;

}

else

{

// +2 to compensate 2*EPWMCLK delay to synchronize EPWM_master and EPWM_slave, +1 to compensate dir

phase = (uint16_t)((float)(EPwm4Regs.TBPRD) * (1-aPhase)) + 3;

dir = 1;

}

}

else

{

// saw-tooth

// +2 co compensate EPWM clk delay, +1 to compensate dir

phase = (uint16_t)(((float)EPwm4Regs.TBPRD+1) * (1-aPhase)) + 3;

if(phase > EPwm4Regs.TBPRD)

{

phase = 0;

}

dir = 0;

}

EPwm4Regs.TBPHS.bit.TBPHS= phase;

EPwm4Regs.TBCTL.bit.PHSDIR = dir;

}

/******** Controling SR functions ************/

static void SynchrRectOnEventsTurnOff(void)

{

//when modes disabled, then set outputs low

//SR A (EPWM 7A)

EPwm7Regs.AQCTLA2.bit.T1D = AQ_CLEAR;

EPwm7Regs.AQCTLA2.bit.T1U = AQ_CLEAR;

EPwm7Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm7Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm7Regs.AQCTLA.bit.PRD = AQ_NO_ACTION;

EPwm7Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION;

//SR B (EPWM 7B)

EPwm7Regs.AQCTLB2.bit.T1U = AQ_CLEAR;

EPwm7Regs.AQCTLB.bit.CAU = AQ_CLEAR;

EPwm7Regs.AQCTLB2.bit.T1D = AQ_CLEAR;

EPwm7Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm7Regs.AQCTLB.bit.PRD = AQ_NO_ACTION;

EPwm7Regs.AQCTLB.bit.ZRO = AQ_NO_ACTION;

//SR B (EPWM 8A)

EPwm8Regs.AQCTLA2.bit.T1U = AQ_CLEAR;

EPwm8Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm8Regs.AQCTLA2.bit.T1D = AQ_CLEAR;

EPwm8Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm8Regs.AQCTLA.bit.PRD = AQ_NO_ACTION;

EPwm8Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION;

}

static void SynchrRectOnEventsConfig(uint16_t srMode,

uint16_t shift)

{

/* srMode provided with SR Modulator logic */

switch(srMode)

{

case 1u:

/* when SR for low currents */

/* when shift below threshold */

if(shift == 1u)

{

EPwm7Regs.AQCTLA2.bit.T1U = AQ_SET;

EPwm7Regs.AQCTLA2.bit.T1D = AQ_NO_ACTION;

EPwm7Regs.AQCTLB2.bit.T1D = AQ_SET;

EPwm7Regs.AQCTLB2.bit.T1U = AQ_NO_ACTION;

EPwm8Regs.AQCTLA2.bit.T1D = AQ_SET;

EPwm8Regs.AQCTLA2.bit.T1U = AQ_NO_ACTION;

EPwm7Regs.AQCTLA.bit.PRD = AQ_NO_ACTION;

}

else

{

EPwm7Regs.AQCTLA2.bit.T1D = AQ_SET;

EPwm7Regs.AQCTLA2.bit.T1U = AQ_NO_ACTION;

EPwm7Regs.AQCTLB2.bit.T1D = AQ_NO_ACTION;

EPwm7Regs.AQCTLB2.bit.T1U = AQ_SET;

EPwm8Regs.AQCTLA2.bit.T1U = AQ_SET;

EPwm8Regs.AQCTLA2.bit.T1D = AQ_NO_ACTION;

//to deal with wrong pwm for 1 epwmclk

EPwm7Regs.AQCTLA.bit.PRD = AQ_CLEAR;

}

/* independent actions from phase shift */

EPwm7Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm7Regs.AQCTLA.bit.CAD = AQ_NO_ACTION;

EPwm7Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm7Regs.AQCTLB.bit.CAU = AQ_NO_ACTION;

EPwm8Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm8Regs.AQCTLA.bit.CAU = AQ_NO_ACTION;

break;

case 2u:

/* when SR for high currents */

/* when shift below threshold */

if(shift == 1u)

{

EPwm7Regs.AQCTLA2.bit.T1D = AQ_CLEAR;

EPwm7Regs.AQCTLA2.bit.T1U = AQ_NO_ACTION;

EPwm7Regs.AQCTLB2.bit.T1U = AQ_CLEAR;

EPwm7Regs.AQCTLB2.bit.T1D = AQ_NO_ACTION;

EPwm8Regs.AQCTLA2.bit.T1U = AQ_CLEAR;

EPwm8Regs.AQCTLA2.bit.T1D = AQ_NO_ACTION;

// EPwm7Regs.AQCTLA.bit.PRD = AQ_NO_ACTION;

else

{

EPwm7Regs.AQCTLA2.bit.T1D = AQ_NO_ACTION;

EPwm7Regs.AQCTLA2.bit.T1U = AQ_CLEAR;

EPwm7Regs.AQCTLB2.bit.T1D = AQ_CLEAR;

EPwm7Regs.AQCTLB2.bit.T1U = AQ_NO_ACTION;

EPwm8Regs.AQCTLA2.bit.T1U = AQ_NO_ACTION;

EPwm8Regs.AQCTLA2.bit.T1D = AQ_CLEAR;

}

/* independent actions from phase shift */

EPwm7Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm7Regs.AQCTLA.bit.CAU = AQ_NO_ACTION;

EPwm7Regs.AQCTLB.bit.CAU = AQ_SET;

EPwm7Regs.AQCTLB.bit.CAD = AQ_NO_ACTION;

EPwm8Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm8Regs.AQCTLA.bit.CAD = AQ_NO_ACTION;

break;

default:

/*SR disabled */

SynchrRectOnEventsTurnOff();

break;

}

}

void ControlSR(uint16_t srMode, bool bursMode)

{

EALLOW;

uint16_t phaseVal = EPwm4Regs.TBPHS.bit.TBPHS;

/* to control synchronous rectifier */

EPwm7Regs.CMPA.bit.CMPA = (uint16_t)((float)EPwm7Regs.TBPRD * 0.5f);

EPwm8Regs.CMPA.bit.CMPA = (uint16_t)((float)EPwm8Regs.TBPRD * 0.5f);

EPwm7Regs.TBPHS.all = 0x0u;

EPwm8Regs.TBPHS.all = 0x0u;

EPwm4Regs.CMPB.bit.CMPB = EPwm4Regs.CMPA.bit.CMPA;

uint16_t phaseThrshld = (uint16_t)((float)EPwm4Regs.TBPRD * 0.5f) + 3u;

if(phaseVal < phaseThrshld)

{

SynchrRectOnEventsConfig(srMode, 1u);

}

else

{

SynchrRectOnEventsConfig(srMode, 2u);

}

/* when burst mode active (frequency of legs is 50 kHz)*/

if( bursMode == true )

{

/* disable SR when burst mode active */

SynchrRectOnEventsTurnOff();

}

EDIS;

/******** END OF NATIVE CODE step : SR on events config ******/

}Hi Dawid,

Have you tried using global load? This would ensure that your updated action qualifer settings for EPWM7 and new phase shift for EPWM4 are both loaded at EPWM TBCTR = 0.

Another option that may be easier to implement is to use the CLB to generate your desired EPWM7 output. You could use the FSM in the CLB to trigger a rising edge on EPWM7 output on any rising edge of EPWM1, and a falling edge of EPWM7 output on any rising edge of EPWM4. This may be more reliable than changing your action qualifer settings for EPWM7 on the fly.

Thank you,

Luke

Hi

I tried to set global load, but it doesn't help. Here is my configuration:

/* global load setting */ // Sync source ePWM1 settings EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_CMPA_CMPAHR|EPWM_GL_REGISTER_CMPB_CMPBHR| EPWM_GL_REGISTER_AQCTLA_AQCTLA2); EPWM_setGlobalLoadTrigger(EPWM1_BASE, EPWM_GL_LOAD_PULSE_CNTR_PERIOD); EPWM_enableGlobalLoadOneShotMode(EPWM1_BASE); EPWM_enableGlobalLoad(EPWM1_BASE); // Sync receiver ePWM4 settings EPWM_enableGlobalLoadRegisters(EPWM4_BASE, EPWM_GL_REGISTER_CMPA_CMPAHR|EPWM_GL_REGISTER_CMPB_CMPBHR| EPWM_GL_REGISTER_AQCTLA_AQCTLA2); EPWM_setGlobalLoadTrigger(EPWM4_BASE, EPWM_GL_LOAD_PULSE_SYNC); EPWM_enableGlobalLoadOneShotMode(EPWM4_BASE); EPWM_enableGlobalLoad(EPWM4_BASE); EPWM_setupEPWMLinks(EPWM4_BASE, EPWM_LINK_WITH_EPWM_1, EPWM_LINK_GLDCTL2); // Sync receiver ePWM7 settings EPWM_enableGlobalLoadRegisters(EPWM7_BASE, EPWM_GL_REGISTER_CMPA_CMPAHR|EPWM_GL_REGISTER_CMPB_CMPBHR| EPWM_GL_REGISTER_AQCTLA_AQCTLA2); EPWM_setGlobalLoadTrigger(EPWM7_BASE, EPWM_GL_LOAD_PULSE_SYNC_OR_CNTR_ZERO); EPWM_enableGlobalLoadOneShotMode(EPWM7_BASE); EPWM_enableGlobalLoad(EPWM7_BASE); EPWM_setupEPWMLinks(EPWM7_BASE, EPWM_LINK_WITH_EPWM_1, EPWM_LINK_GLDCTL2); // Sync receiver ePWM8 settings EPWM_enableGlobalLoadRegisters(EPWM8_BASE, EPWM_GL_REGISTER_CMPA_CMPAHR|EPWM_GL_REGISTER_CMPB_CMPBHR| EPWM_GL_REGISTER_AQCTLA_AQCTLA2); EPWM_setGlobalLoadTrigger(EPWM8_BASE, EPWM_GL_LOAD_PULSE_SYNC_OR_CNTR_ZERO); EPWM_enableGlobalLoadOneShotMode(EPWM8_BASE); EPWM_enableGlobalLoad(EPWM8_BASE); EPWM_setupEPWMLinks(EPWM8_BASE, EPWM_LINK_WITH_EPWM_1, EPWM_LINK_GLDCTL2); /* During controling sr */ EPWM_setGlobalLoadOneShotLatch(EPWM1_BASE); EPWM_setGlobalLoadOneShotLatch(EPWM4_BASE); EPWM_setGlobalLoadOneShotLatch(EPWM7_BASE); EPWM_setGlobalLoadOneShotLatch(EPWM8_BASE);

I didn't considered using CLB. Is it possible to introduce some delay with CLB, like with deadtime generator? Could you point me some examples which would be useful if I want to try this?

Best regards

Dawid

Hi Dawid,

The CLB provides the option to override the outputs of individual submodules within EPWM. For example, you could override the output of the action qualifier module of EPWM7, and then apply dead-band to that output using the dead-band module of EPWM.

We have examples in C2000Ware for using the CLB. You would need to use the output override function to override the EPWM_AQ output.

Hi,

Sorry I made a mistake at the beginning,

My device is actually TMS320F280041, so unfortunately it does not have CLB. I must try then solution on epwms

Hi Dawid,

I have another proposal. Instead of using EPWM4B syncout to generate a T1 event, you can perform the following configuration:

This will effectively cause EPWM8A output to go low whenever EPWM4 TBCTR = CMPB on down-count only, so you will not need to update your action qualifer settings for EPWM8 during run-time. The only disadvantage to this approach is you will not be able to apply falling edge delay on EPWM8, since the output is overridden by the trip zone module, however rising edge delay will still be available.

Thank you,

Luke