Part Number: TMS320F28379D

Hi,

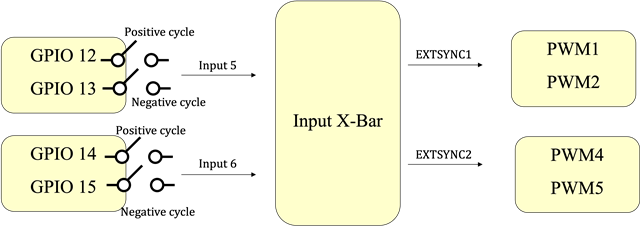

I have 4 signals which I am routing to Gpio 12,13,14 and 15 (TZ1-TZ4). I want to use these signals for giving synchronization pulse (I will route them to EXTSYNC1 and EXTSYNC2). While going through the technical reference, I saw that TZ1-TZ3 is routed to ePWM but TZ4 is not (pg 1866). I still want to use TZ4 for synchronization. Is there a way this could be possible? Or if there is another pin from where I can send pulse to either EXTSYNC1 or EXTSYNC2?

Thanks