Hi,

We have been using the provided pre-compiled library with some success but now we are moving the functionality into a more complicated design has resource restrictions and need to better understand the source code to make sure it uses the correct resources and configures the clocks properly.

Our design now requires that the CLB clock be 100 MHz and the PWM clock be 200 MHz, in addition our new design uses EPWM1 and we are uncertain what would need to change to properly support this.

1) In the example design in PM_bissc_setupPeriph EPWM1A is connected to CLB_IN0,6 and 7 of CLB3 and CLB4. In the example EPWM1 is never configured. What is the intended behavior of this signal? What does it do?

2) In the example design in PM_bissc_configureCLBLength CLB_ADDR_COUNTER_1_MATCH1 in CLB4_BASE is forced to 200. What is this value? If the CLB is clocked at 100MHz should this change to 100?

3) When we pass 25 into PM_bissc_setFreq we get a 4 MHz BiSS-C output clock, the documentation and comments indicate that this should be 2 MHz. clock frequency = SYSCLK/(4*BISSC_FREQ_DIVIDER). Our SYSCLK is 200 MHz, seems like we are now off by a factor of 2?

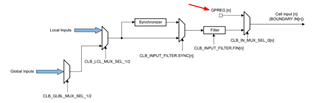

4) I am sure this is a stupid question, Clock is clearly coming out on the correct pins and the pins are configured to connect to EPWM4A and 4B. When we set things up we use the trip zone to force the outputs high but I don't understand in the code how the CLB talks to the EPWM. The EPWM4 is enabled but other than the tripzones is not configured. How does the CLB control the EPWM? How do they physically connect, i.e. what CLB outputs connect to EPWM inputs?

Thank you,

Jennifer