- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I couldn't find any examples, so that may suggest this is just a bad idea..

Let's say I need to switch from a normal ADC clock prescaler of /8 to /4 for some specific conversions and then return back to /8 (please don't ask why, let's just assume this is how it must be).

What would be the correct steps reconfigure the ADC clock prescaler for the /4 conversion and then get it back to /8?

Some questions:

Does the ADC need to be disabled when being reconfigured? If the conversion must stop, then I think the other questions become moot as there would be a 500us enable conversion delay needed.

If the adc clock prescaler can be changed while active, is there a need to wait for a settling period?

I can see both yes and no...

Since it's just changing prescaler of a stable clock, I could maybe see no need for a delay. But I don't believe this is correct.

Depending on the architecture, I could see there may be problems with in-flight conversions or new conversions which hit before the new prescaler value gets in rhythm.

Hello JJ,

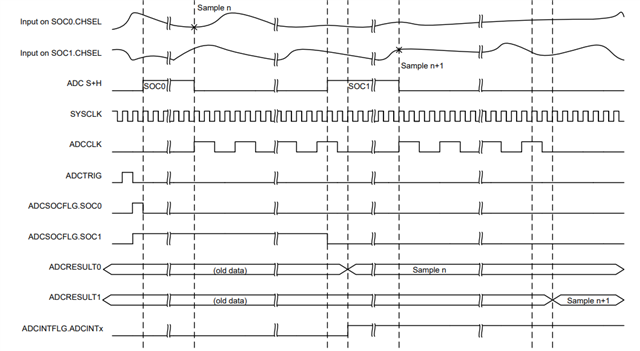

ADCCLK is only active during the conversion phase (from the end of sample-and-hold to end of conversion). It should be fine to reconfigure the prescaler in between conversions as necessary; there is no need to power down the converter first. This clock is prescaled down from SYSCLK - it is not an independent clock, so there is no settling time involved. Think of ADCCLK as a divided-down derivative of SYSCLK that is only gated on when the ADC is in the conversion phase. See the following timing diagram (taken from the device TRM - ADC Chapter > ADC Timings):

That said, you should *not* change the prescaler in the middle of a conversion; there could be unexpected results if you do so. Also, when messing with clock prescaler values, be sure to avoid creating an asynchronous operation condition between multiple ADCs that should otherwise be operating synchronously. If you change the prescale value of one ADC but not the others, then your conversions could become asynchronous, and this causes inaccuracy in results.

Best regards,

Ibukun