Part Number: TMS320F28375S

Other Parts Discussed in Thread: C2000WARE, SYSBIOS

Dear Sir or Madam

We migrated our firmware to eabi from the coff format. Or at least, we are trying to. Whenever we flash it, it crashes even before it reaches the main. More precisely, in the UserInit function which is called at reset, we copy some progam code from flash to memory. When we debug in assembly step we see, that the function jumps at a random step to the address 0x3FE493 and stops. The memcpy is basically a loop with two MOV instructions and a branch if not equal to zero instruction. The memory range of the RAM is enough large to store all data from the Flash. IT is interesting, that it happens only then copying the objects from the IQmath library.

Two times debugging showed, that it crashes during copying the functions of the the updated IQmath_fpu32_eabi library. It is not exact the same address, but it is always within the range, where the IQmath functions are stored.

There is a similar thread which did not help, since it only references to the manual, which we of course considered: https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1244672/tms320f28075-migration-from-coff-to-eabi-crash-during-_c_int00

I compared the new .eabi map file with the coff.abi file. There were some changed which seemed to be strange for me, but I have no idea if they have influence on the issue or if they are correct.

- In the eabi.map file PieVectTable is listed with 0 length and have only DSECT at the attributes/input section, whereas the coff format have a length > 0 and also F2837xS_globalvariables referred.

- AdcResultFileD is missing in the eabi.map file

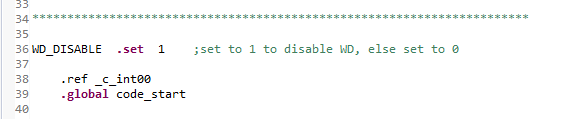

- CodeStartBranch.asm is missing in .map file

- In eabi.map: There is an additinoal entry in Linker generated copy tableds: ___TI__cinit_table

This list is quite random and I assume, there are some more differences. Maybe it helps for the issue to solve.

At the end of the post I inserted all important files for this issue.

thank you and best regards

Robert

The following code shows the User Init function:

/*----------------------------------------------------------------------------

function: UserInit

----------------------------------------------------------------------------*/

extern "C" void UserInit()

{

// SYS/BIO UserInit function.

//

// This is the user initialization function to be specified in

// the SYS/BIOS configuration file (Startup -> User reset function)

//

// Use this function to copy flash sections to RAM

//

// @note Will be called before main().

//--- Copy all Flash sections that need to run in RAM

memcpy(&RamfuncsRunStart, &RamfuncsLoadStart, (size_t)&RamfuncsLoadSize);

//--- Section secureRamFuncs contains user defined code that runs from CSM secured RAM

memcpy(&secRamRunStart, &secRamLoadStart, (size_t)&secRamLoadSize);

}

Snipped of the .cmd file:

codestart : > FLASHE PAGE = 0

ramfuncs : LOAD = FLASHE | FLASHF | FLASHG | FLASHH | FLASHI |

FLASHJ | FLASHK | FLASHL | FLASHM | FLASHN PAGE = 0

RUN = D01SARAM PAGE = 0

RUN_START(RamfuncsRunStart),

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize)

{ -l IQmath_fpu32_eabi.lib

(IQmath)

}

#ifdef __TI_COMPILER_VERSION

#if __TI_COMPILER_VERSION >= 15009000

.TI.ramfunc : LOAD = FLASHE | FLASHF | FLASHG | FLASHH | FLASHI |

FLASHJ | FLASHK | FLASHL | FLASHM | FLASHN PAGE = 0,

RUN = LS05SARAM PAGE = 1,

table(BINIT)

#endif

#endif

IQmathTables : > FLASHE | FLASHF | FLASHG | FLASHH | FLASHI |

FLASHJ | FLASHK | FLASHL | FLASHM | FLASHN PAGE = 0

Snipped of map file:

ramfuncs 0 00088010 00000ae3 RUN ADDR = 0000b000 00088010 000001af MotionControl.obj (ramfuncs:_ZN13MotionControl3isrEv) 000881bf 000000a0 MotionControlPwmIRQ.obj (ramfuncs:_ZN19MotionControlPwmIrq6pwmIrqER19PwmControlParamer) 0008825f 0000008b MotionControlPwmIRQ.obj (ramfuncs:_ZN19MotionControlPwmIrq24holdPositionStaHandlerENS_9EPwmEvenR19PwmControlParamer) 000882ea 00000089 PWM.obj (ramfuncs:_ZN6PWMGEN6setPWMERK19PwmControlParamer) 00088373 00000079 PIDController.obj (ramfuncs:_ZN13PIDController9calculaEll) 000883ec 00000069 MotionControlPwmIRQ.obj (ramfuncs:_ZN19MotionControlPwmIrq23safeHoldPosStaHandlerENS_9EPwmEvenR19PwmControlParamer) 00088455 00000064 MotionControlPwmIRQ.obj (ramfuncs:_ZN19MotionControlPwmIrq16moveStaHandlerENS_9EPwmEvenR19PwmControlParamer) 000884b9 0000005e StatisticModuleExnded.obj (ramfuncs:_ZN23StatisticModuleExnded8addValueEv) 00088517 0000004c EncoderBase.obj (ramfuncs:_ZNK11EncoderBase8getThetaEPl) 00088563 00000042 Absoluncoder2.obj (ramfuncs:_ZN15Absoluncoder217calculaPositionEv) 000885a5 0000003b Absoluncoder.obj (ramfuncs:_ZN14Absoluncoder17calculaPositionEv) 000885e0 0000003b QEP.obj (ramfuncs:_ZN3QEP17calculaPositionEv) 0008861b 00000036 MotionControlFsmBase.obj (ramfuncs:_ZN20MotionControlFsmBase24calculaAllEncPositionsEv) 00088651 00000023 TwinQep.obj (ramfuncs:_ZN7TWINQEP17calculaPositionEv) 00088674 0000001e OverCurrent.obj (ramfuncs:_ZN11OverCurrent9calculaEl) 00088692 00000018 DataLogger.obj (ramfuncs:_ZN10DataLogger8logValueEl) 000886aa 00000018 StatisticModuleLight.obj (ramfuncs:_ZN20StatisticModuleLight8addValueEv) 000886c2 00000010 SysmTimers.obj (ramfuncs:SysmTimers_delay_us) 000886d2 0000000e StatisticModuleExnded.obj (ramfuncs:_ZN23StatisticModuleExnded13prepareMeanIQEl) 000886e0 0000000e StatisticModuleExnded.obj (ramfuncs:_ZN23StatisticModuleExnded14prepareMeanInl) 000886ee 00000009 ExndedstPointManager.obj (ramfuncs:_ZN24ExndedstPointManager20calculaMinMaxValueERNS_20ExndedstPointDefE) 000886f7 00000009 ExndedstPointManager.obj (ramfuncs:_ZN24ExndedstPointManager20updaFaststPointsEv) 00088700 00000009 ExndedstPointManager.obj (ramfuncs:_ZN24ExndedstPointManager20updaSlowstPointsEv) 00088709 00000008 MotionControl.obj (ramfuncs:ADCINT_A1_ISR) 00088711 00000006 CanDriver.obj (ramfuncs:ECAN0INTB_ISR) 00088717 00000006 CanDriver.obj (ramfuncs:ECAN1INTB_ISR) 0008871d 00000003 Absoluncoder.obj (ramfuncs:_ZNK11EncoderBase11getPositionEv) 00088720 000000e2 IQmath_fpu32_eabi.lib : IQNtoa.obj (IQmath) 00088802 00000047 : IQ12div.obj (IQmath) 00088849 00000047 : IQ15div.obj (IQmath) 00088890 00000047 : IQ16div.obj (IQmath) 000888d7 00000047 : IQ17div.obj (IQmath) 0008891e 00000047 : IQ20div.obj (IQmath) 00088965 00000047 : IQ26div.obj (IQmath) 000889ac 00000042 : IQ16sqrt.obj (IQmath) 000889ee 00000032 : IQ28sin.obj (IQmath) 00088a20 00000030 : IQ28cos.obj (IQmath) 00088a50 0000002a : IQ26sinPU.obj (IQmath) 00088a7a 00000028 : IQ26cosPU.obj (IQmath) 00088aa2 00000016 : IQ16toF.obj (IQmath) 00088ab8 00000016 : IQ26toF.obj (IQmath) 00088ace 00000016 : IQ28toF.obj (IQmath) 00088ae4 00000009 : IQ16int.obj (IQmath) 00088aed 00000006 : iqntoa_get_frac_c.obj (IQmath)

the complete cmd file is here:

MEMORY

{

PAGE 0 : /* Program Memory */

D01SARAM : origin = 0x00B000, length = 0x001000

/* BEGIN is used for the "boot to FLASH" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000002

/* Flash sectors */

#ifdef BOOTLOADER

/* IMAGE Header adress range */

IMAGE_HEADER : origin = 0x080010, length = 0x000010

//FLASHA - FLASHC is used for Bootloader

FLASHA : origin = 0x080020, length = 0x001FE0 /* on-chip Flash */

FLASHB : origin = 0x082000, length = 0x002000 /* on-chip Flash */

FLASHC : origin = 0x084000, length = 0x001FFE /* on-chip Flash, last two bytes of sector C are reserved for bootloader CRC */

#else

/* IMAGE Header adress range */

IMAGE_HEADER : origin = 0x088000, length = 0x000010

// FLASHE - FLASHN is used for Application

FLASHE : origin = 0x088010, length = 0x007FF0 /* on-chip Flash */

FLASHF : origin = 0x090000, length = 0x008000 /* on-chip Flash */

FLASHG : origin = 0x098000, length = 0x008000 /* on-chip Flash */

FLASHH : origin = 0x0A0000, length = 0x008000 /* on-chip Flash */

FLASHI : origin = 0x0A8000, length = 0x008000 /* on-chip Flash */

FLASHJ : origin = 0x0B0000, length = 0x008000 /* on-chip Flash */

FLASHK : origin = 0x0B8000, length = 0x002000 /* on-chip Flash */

FLASHL : origin = 0x0BA000, length = 0x002000 /* on-chip Flash */

FLASHM : origin = 0x0BC000, length = 0x002000 /* on-chip Flash */

FLASHN : origin = 0x0BE000, length = 0x001FFE /* on-chip Flash , last two bytes of sector N are reserved for bootloader CRC */

#endif

// FLASHD is used for shared data

FLASHD : origin = 0x086000, length = 0x001C00 /* on-chip Flash */

USEROTPEMU : origin = 0x087C00, length = 0x000400 /* Mapping of the old user OTP memory */

BOOTROM : origin = 0x3FF27C, length = 0x000D44

RESET : origin = 0x3FFFC0, length = 0x000002

PAGE 1 : /* Data Memory */

BOOT_RSVD : origin = 0x000002, length = 0x000122 /* Part of M0, BOOT rom

will use this for

stack */

M01SARAM : origin = 0x000124, length = 0x0006D6 /* on-chip RAM */

// M01SARAM_RSVD : origin = 0x0007F8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

LS05SARAM : origin = 0x008010, length = 0x003000 /* on-chip RAM */

/* on-chip Global shared RAMs */

BOOT_PARAMETER : origin = 0x00C000, length = 0x000010

RAMGS0 : origin = 0x00C010, length = 0x000FF0

RAMGS1 : origin = 0x00D000, length = 0x001000

//RAMGS2 : origin = 0x00E000, length = 0x001000 // Used for overlay

RAMGS3 : origin = 0x00F000, length = 0x002000

//RAMGS4 : origin = 0x010000, length = 0x001000 // merged with RAMGS3 to fit the DataLogger.obj

RAMGS5 : origin = 0x011000, length = 0x001000

RAMGS6 : origin = 0x012000, length = 0x001000

RAMGS7 : origin = 0x013000, length = 0x000FF8

// RAMGS7_RSVD : origin = 0x013FF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

PAGE 2: /* Program Memory Overlay1 (RAMGS2) */

LOVERLAY : origin = 0x00E000, length = 0x001000 /* BLDC motor specific programm area */

PAGE 3: /* Program Memory Overlay2 (RAMGS2) */

LOVERLAY : origin = 0x00E000, length = 0x001000 /* FOC motor specific programm area */

PAGE 4: /* Program Memory Overlay3 (RAMGS2) */

LOVERLAY : origin = 0x00E000, length = 0x001000 /* DC motor specific programm area */

}