Part Number: TMS320F2800137

Hi,

I have some general questions.

The data will only transfered from RXSHF to SCIXBUF if no receive error RXERROR (bits 5-2: BRKDT, FE, OE, and PE) occurs, ok?

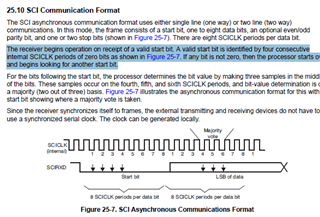

RXSHF begin receiving with the start bit? What is the condition to detect a start bit? Long time high (how many SCICLK???) followed by by four consecutive

internal SCICLK periods of zero bits.

After an detected error the RXSHF will be cleared? At each new start bit the RXSHF will be cleared?

Two bit error can't be detected, right?

Regards, Holger