Part Number: TMS320F28379D

Hi,.

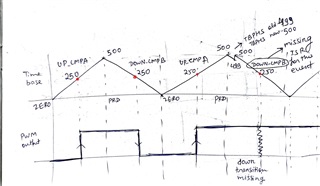

I'm using F28379D controller for my application of controlling two full bridge converter. In this, I am using 4-EPWMs. Im keeping EPWM1 as master and which will generate syncout event when EPWM_SYNC_OUT_PULSE_ON_COUNTER_ZERO. The problem I'm facing was (focusing only on EPWM3), when I'm changing the phase shift value from 0 to 1 in TBPHS of EPWM3, it's missing one entire cycle of pulse. I have tried with many variety of values and found that it happens only when I shift from 0 to other values. I have read some E2E forums and TRM, but didn't getting proper solution for this. The configuration which I've used in EPWM3 was given below, have a look at it. Kindly provide me the solution, why it's happening and how to resolve this. Thanks

EPWM3:

//

// Set-up TBCLK

//

EPWM_setTimeEPWM3_BASEPeriod(EPWM3_BASE, EPWM_TIMER_TBPRD-1);

EPWM_setPhaseShift(EPWM3_BASE, 0U);

EPWM_setTimeEPWM3_BASECounter(EPWM3_BASE, 0U);

//

// Set Compare values

//

EPWM_setCounterCompareValue(EPWM3_BASE,

EPWM_COUNTER_COMPARE_A,

(EPWM_TIMER_TBPRD/2)-1);

EPWM_setCounterCompareValue(EPWM3_BASE,

EPWM_COUNTER_COMPARE_B,

(EPWM_TIMER_TBPRD/2)-1);

//

// Set up counter mode

//

EPWM_setTimeEPWM3_BASECounterMode(EPWM3_BASE, EPWM_COUNTER_MODE_UP);

EPWM_disablePhaseShiftLoad(EPWM3_BASE);

EPWM_setClockPrescaler(EPWM3_BASE,

EPWM_CLOCK_DIVIDER_1,

EPWM_HSCLOCK_DIVIDER_1);

//

// Set up shadowing

//

EPWM_setCounterCompareShadowLoadMode(EPWM3_BASE,

EPWM_COUNTER_COMPARE_A,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM3_BASE,

EPWM_COUNTER_COMPARE_B,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setDeadBandControlShadowLoadMode(EPWM3_BASE, EPWM_DB_LOAD_ON_CNTR_ZERO);

//

// Set actions

//

EPWM_setActionQualifierAction(EPWM3_BASE,

EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_HIGH,

EPWM_AQ_OUTPUT_ON_TIMEEPWM3_BASE_ZERO);

EPWM_setActionQualifierAction(EPWM3_BASE,

EPWM_AQ_OUTPUT_B,

EPWM_AQ_OUTPUT_HIGH,

EPWM_AQ_OUTPUT_ON_TIMEEPWM3_BASE_ZERO);

EPWM_setActionQualifierAction(EPWM3_BASE,

EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEEPWM3_BASE_UP_CMPA);

EPWM_setActionQualifierAction(EPWM3_BASE,

EPWM_AQ_OUTPUT_B,

EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEEPWM3_BASE_UP_CMPB);

//

// ePWM1 SYNCO is generated on CTR=0

//

EPWM_setSyncOutPulseMode(EPWM1_BASE, EPWM_SYNC_OUT_PULSE_ON_COUNTER_ZERO);

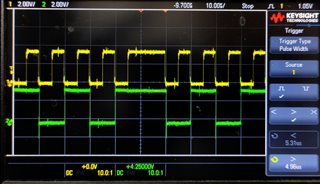

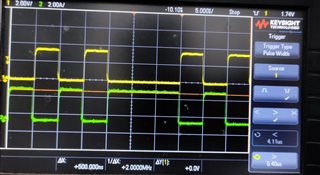

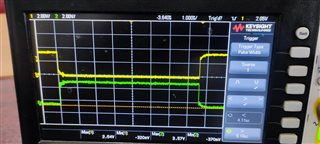

Here i've attached the missing pulse event. Yellow - EPWM3A, Green - EPWM3B both are complementry signals.

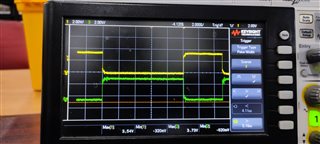

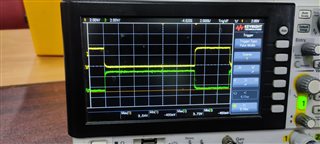

Image showing PWM4A during phase transition from499 to 500.

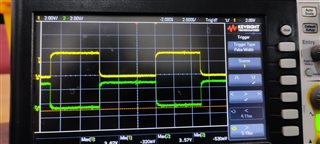

Image showing PWM4A during phase transition from499 to 500.