Hi,

For the SYNCOSEL option given in EPWM modules, how can we specify the direction of count while choosing CMPB option. I am using an updown counter mode in my EPWM configuration. I want to create a syncout from EPWM1 at a specific CTR value while down counting.

5-4 SYNCOSEL -Sync Output Select

00: EPWMxSYNCI / SWFSYNC

01: CTR = zero: Time-base counter equal to zero (TBCTR = 0x00)

10: CTR = CMPB : Time-base counter equal to counter-compare B

(TBCTR = CMPB)

11: EPWMXSYNCO is defined by TBCTL2[SYNCOSELX]

Reset type: SYSRSn

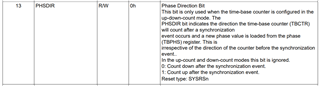

Out of the above options, how is it possible to define the direction of counting while choosing option -10 (CTR = CMPB ).

Any help would be appreciated.

Thanks

Deepthi