Other Parts Discussed in Thread: C2000WARE

Hello I'm experiencing a duty cycle issue during the phase transition, and I would like to hear your opinions.

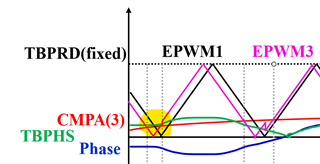

I'm using updown counter for all EPWM channel. The orange represents EPWM3, and the gray represents EPWM4 channels. I've set EPWM1 as a reference to adjust the phase of EPWM3 and EPWM4. In the section of the image, the duty cycle of EPWM3 is approximately d3=0.1, and EPWM4 should switch complementarily with 1-d3.

However, the issue arises in the highlighted red rectangle. The duty cycle of EPWM3 should be around 0.1, but suddenly it becomes 1 in that region. Despite limiting the duty cycle of EPWM to a maximum of 0.5, it unexpectedly reaches 1. This problem doesn't persist but occurs sporadically even though it generally operates well.

This problem seems to occur when using phase shift, and it works fine when phase shift is not applied. Moreover, during this time, when the phase transitions from positive to negative, it seems to have an impact.

please see the code below.

-------------------------------------------------------------------------------------------------------------------------

//EPWM set

// Updown

ePWM_Regs[ch]->AQCTLA.bit.CAD = AQ_SET;

ePWM_Regs[ch]->AQCTLA.bit.CAU = AQ_CLEAR;

ePWM_Regs[ch]->AQCTLB.bit.CAD = AQ_SET;

ePWM_Regs[ch]->AQCTLB.bit.CAU = AQ_CLEAR;

if(ch==1 ){

ePWM_Regs[ch]->TBCTL.bit.PHSEN = 0;//TB_DISABLE;

ePWM_Regs[ch]->TBCTL.bit.SYNCOSEL =1;// TB_CTR_ZERO;

}

else if(ch!=1) {

ePWM_Regs[ch]->TBCTL.bit.PHSEN = 1;//TB_ENABLE;

ePWM_Regs[ch]->TBCTL.bit.SYNCOSEL = 0;//TB_SYNC_IN;

}

SyncSocRegs.SYNCSELECT.bit.SYNCOUT = 0x2; //(enable)

// Setup TBCLK

ePWM_Regs[ch]->TBCTL.bit.CTRMODE = 2;//TB_COUNT_UPDOWN; // Count up-down

ePWM_Regs[ch]->TBCTL.bit.PRDLD = 0;//TB_SHADOW;

ePWM_Regs[ch]->TBCTL.bit.HSPCLKDIV = 0;//TB_DIV1;

ePWM_Regs[ch]->CMPCTL.bit.SHDWAMODE = 0;//CC_SHADOW;

ePWM_Regs[ch]->CMPCTL.bit.SHDWBMODE = 0;//CC_SHADOW;

ePWM_Regs[ch]->CMPCTL.bit.LOADAMODE = 0;//CC_CTR_ZERO;

ePWM_Regs[ch]->CMPCTL.bit.LOADBMODE = 0;//CC_CTR_ZERO;

ePWM_Regs[ch]->DBCTL.bit.IN_MODE = 2;//DBA_RED_DBB_FED;

ePWM_Regs[ch]->DBCTL.bit.POLSEL = 2;//DB_ACTV_HIC;

ePWM_Regs[ch]->DBCTL.bit.OUT_MODE = 3;//DB_FULL_ENABLE;

----------------------------------------------------------------------------------------

//phase shift setting

if(phase == 0) ePWM_Regs[ch]->TBPHS.bit.TBPHS = 0;

else if(phase > 0){

ePWM_Regs[ch]->TBCTL.bit.PHSDIR = 0;

ePWM_Regs[ch]->TBPHS.bit.TBPHS = (int16)((float32)ePWM_Regs[ch]->TBPRD * phase * 0.00277777);

}

else {

ePWM_Regs[ch]->TBCTL.bit.PHSDIR = 1;

ePWM_Regs[ch]->TBPHS.bit.TBPHS = (int16)((float32)ePWM_Regs[ch]->TBPRD * -phase * 0.00277777);

}

-----------------------------------------------------------------------------------------------------

//duty setting

ePWM_Regs[ch]->CMPA.bit.CMPA = (Uint32)((float32)ePWM_Regs[ch]->TBPRD * duty);

---------------------------------------------------------------------------------------------------------