Other Parts Discussed in Thread: SYSCONFIG

Hi Support,

My Assigned Focus Customer notes:

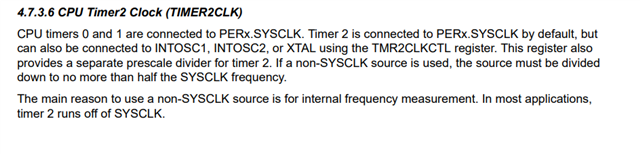

We’re not using Sysconfig, and I am setting the TMR2CLKCTL to the correct setting (using a DriverLib call to CPUTimer_selectClockSource, with a clock source of CPUTIMER_CLOCK_SOURCE_INTOSC2).

After boot, we setup our system to use INTOSC1 as the clock source for the PLL. We use a call to SysCtl_setClock to produce a SYSCLK of 120MH. No problem with any of that.

Later in the code, we setup TIMER0 (using SYSCLK as its source) to produce a 1 kHz tick. No problem with any of that.

And if I setup TIMER2 the same way (SYSCLK as source), the timer output is correct.

When I switch TIMER2 to use INTOSC1 as it’s source (CPUTimer_selectClockSource w/ clock source of CPUTIMER_CLOCK_SOURCE_INTOSC1) and use the calculated period of 10000, everything is OK – I get the 1 kHz tick, a timer period of 1 ms.

Things start getting strange when I change the code to use INTOSC2 as the TIMER2 source. Same setup as when using INTOSC1. The only change is in the call to CPUTimer_selectClockSource – I change the CPUTIMER_CLOCK_SOURCE_INTOSC1 to be CPUTIMER_CLOCK_SOURCE_INTOSC2. And using the same period count, I end up with TIMER2 firing every 450 ms. A little math and I arrive at a new “period count” of 22. When I use that value instead of the calculated value (10000), I get the desired 1 ms period / 1 kHz tick.

-------------

Your initial reply got me thinking, so I halted the system in the middle of operation and confirmed that TMR2CLKCTL.TMR2CLKSRCSEL was 2, so the call to CPUTimer_selectClockSource seems to do what I expect.

BTW – I also modified one of the simple example apps for the F2800157 (timer_ex1_cputimers) to configure the timers in a similar manner and got the same results, so I’m reasonably confident that it’s not something we’re doing here. I think it’s more likely something we’re not doing, but needs to be done.

I can get some code from the customer offline and send it to you for evaluation, but wanted to get your sanity check first.

Thanks!

Best Regards,

Blake