Other Parts Discussed in Thread: TIDM-DC-DC-BUCK, PMP41081

Hi,

I'm trying to control a 3MHz buck regulator. What are the limitations I can come across at this switching frequency?

The goal it to use peak current mode control and a goal crossover frequency of about 300kHz.

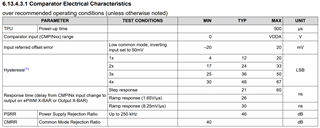

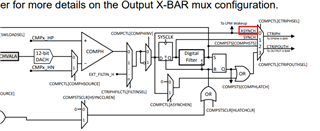

For the current feedback, I was thinking of using a high speed comparator to send a flag to the MCU when the inductor current hits the voltage control threshold. This is because the sample rate is 3.92 MSPS, which is not fast enough to track the inductor ripple. Do you see this being achievable?

Can the C2000 accept an interrupt for the current loop and still maintain control?

What other control schemes have you used other than peak current mode control? Is there a control scheme that highlights the 2000 better than others?

What are some other recommendations you may have that could achieve this?