- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello Experts,

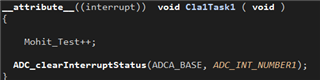

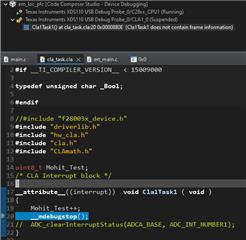

I'm running CLA task on ADC EOC. after adding control loop code into task it is buildable but not working. For confirmation I added a variable for testing and implemented such a way that on every call of CLA task it increments. CLA task is simple as now.

when I run code variable is not incrementing even though added code is commented out. Memory allocation is OK it notifies that linking is done properly.

I'm attaching linker file and map file for your reference below.

Hi Mohit,

Can you instead try adding a __mdebugstop() line into the CLA task and seeing if the CLA ever stops there? You can load the code in the following order to check if the task is being called:

There is also an example in C20000ware where a CLA task is triggered by an ADC event (cla_ex5_adc_just_in_time), can you make sure your setup is similar?

Best Regards,

Delaney

Hello,

Thanks for your reply.

I tried to follow steps which you mentioned above. It is halting at __mdebugstop() but on removing it, CLA core is not working properly.

I checked with example code, it is having same configuration as example for triggering.

please suggest solution for this.

Mohit M

Hi Mohit,

It is halting at __mdebugstop() but on removing it, CLA core is not working properly.

That means that the task is being triggered properly then. What exactly are you seeing not working? Is not incrementing the Mohit_test() variable you are referring to?

Did you make any changes to the linker cmd file from one of the C2000ware provided linker cmd files? If so, what did you change and what was the purpose for changing? It is usually recommended not to change the linker if possible.

Best Regards,

Delaney

Hello,

yes we changed linker file as memory for CLA was limited.

We used linker file of one of the example project which has same application as us. linker file is attched below.

CLA is taking 8.7kb size where upto 8kb code is working fine. is there any limitation? we are using type2 CLA.

MEMORY

{

BEGIN : origin = 0x00080000, length = 0x00000002

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMLS0LS1 : origin = 0x00008000, length = 0x00001000

// RAMLS1 : origin = 0x00008800, length = 0x00000800

RAMLS2LS3LS4LS5LS6 : origin = 0x00009000, length = 0x00002800

// RAMLS3 : origin = 0x00009800, length = 0x00000800

// RAMLS4 : origin = 0x0000A000, length = 0x00000800

// RAMLS5 : origin = 0x0000A800, length = 0x00000800

// RAMLS6 : origin = 0x0000B000, length = 0x00000800

RAMLS7 : origin = 0x0000B800, length = 0x00000800

RAMGS0GS1 : origin = 0x0000C000, length = 0x00002000

// RAMGS1 : origin = 0x0000D000, length = 0x00001000

RAMGS2 : origin = 0x0000E000, length = 0x00001000

RAMGS3 : origin = 0x0000F000, length = 0x00000FF8

// RAMGS3_RSVD : origin = 0x0000FFF8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

BOOTROM : origin = 0x003F8000, length = 0x00007FC0

SECURE_ROM : origin = 0x003F2000, length = 0x00006000

RESET : origin = 0x003FFFC0, length = 0x00000002

/* Flash sectors */

/* BANK 0 */

FLASH_BANK0_SEC0 : origin = 0x080002, length = 0x000FFE

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000

FLASH_BANK0_SEC2_3_4 : origin = 0x082000, length = 0x004000

// FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000

// FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000

// FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000

FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000

FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000

FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x001000

/* BANK 1 */

FLASH_BANK1_SEC0 : origin = 0x090000, length = 0x001000

FLASH_BANK1_SEC1 : origin = 0x091000, length = 0x001000

FLASH_BANK1_SEC2 : origin = 0x092000, length = 0x001000

FLASH_BANK1_SEC3 : origin = 0x093000, length = 0x001000

FLASH_BANK1_SEC4 : origin = 0x094000, length = 0x001000

FLASH_BANK1_SEC5 : origin = 0x095000, length = 0x001000

FLASH_BANK1_SEC6 : origin = 0x096000, length = 0x001000

FLASH_BANK1_SEC7 : origin = 0x097000, length = 0x001000

FLASH_BANK1_SEC8 : origin = 0x098000, length = 0x001000

FLASH_BANK1_SEC9 : origin = 0x099000, length = 0x001000

FLASH_BANK1_SEC10 : origin = 0x09A000, length = 0x001000

FLASH_BANK1_SEC11 : origin = 0x09B000, length = 0x001000

FLASH_BANK1_SEC12 : origin = 0x09C000, length = 0x001000

FLASH_BANK1_SEC13 : origin = 0x09D000, length = 0x001000

FLASH_BANK1_SEC14 : origin = 0x09E000, length = 0x001000

FLASH_BANK1_SEC15 : origin = 0x09F000, length = 0x001000

/* BANK 2 */

FLASH_BANK2_SEC0_SEC1_SEC2 : origin = 0x0A0000, length = 0x003000

// FLASH_BANK2_SEC1 : origin = 0x0A1000, length = 0x001000

// FLASH_BANK2_SEC2 : origin = 0x0A2000, length = 0x001000

FLASH_BANK2_SEC3 : origin = 0x0A3000, length = 0x001000

FLASH_BANK2_SEC4 : origin = 0x0A4000, length = 0x001000

FLASH_BANK2_SEC5 : origin = 0x0A5000, length = 0x001000

FLASH_BANK2_SEC6 : origin = 0x0A6000, length = 0x001000

FLASH_BANK2_SEC7 : origin = 0x0A7000, length = 0x001000

FLASH_BANK2_SEC8 : origin = 0x0A8000, length = 0x001000

FLASH_BANK2_SEC9 : origin = 0x0A9000, length = 0x001000

FLASH_BANK2_SEC10 : origin = 0x0AA000, length = 0x001000

FLASH_BANK2_SEC11 : origin = 0x0AB000, length = 0x001000

FLASH_BANK2_SEC12 : origin = 0x0AC000, length = 0x001000

FLASH_BANK2_SEC13 : origin = 0x0AD000, length = 0x001000

FLASH_BANK2_SEC14 : origin = 0x0AE000, length = 0x001000

FLASH_BANK2_SEC15 : origin = 0x0AF000, length = 0x000FF0

// FLASH_BANK0_SEC15_RSVD : origin = 0x0AFFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

}

SECTIONS

{

.cinit : > FLASH_BANK0_SEC1, ALIGN(4)

.text : >>FLASH_BANK0_SEC2_3_4 , ALIGN(4)

codestart : > BEGIN, ALIGN(4)

.stack : > RAMM1

.switch : > FLASH_BANK0_SEC1, ALIGN(4)

#if defined(__TI_EABI__)

.init_array : > FLASH_BANK0_SEC1, ALIGN(4)

.bss : > RAMGS2

.bss:output : > RAMGS2

.bss:cio : > RAMGS2

.data : > RAMGS2

.sysmem : > RAMGS2

.const : > FLASH_BANK0_SEC6 ALIGN(4)

#else

.pinit : > FLASH_BANK0_SEC1 ALIGN(4)

.ebss : >>RAMLS5 | RAMLS7

.esysmem : > RAMLS7

.cio : > RAMLS5

.econst : > FLASH_BANK0_SEC6

#endif

.reset : > RESET, TYPE = DSECT /* not used, */

dclfuncs : > FLASH_BANK0_SEC1, ALIGN(4)

#if defined(__TI_EABI__)

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK2_SEC0_SEC1_SEC2,

RUN = RAMLS2LS3LS4LS5LS6,

LOAD_START(Cla1ProgLoadStart),

RUN_START(Cla1ProgRunStart),

LOAD_SIZE(Cla1ProgLoadSize),

ALIGN(4)

#else

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK2_SEC0_SEC1_SEC2,

RUN = RAMLS2LS3LS4LS5LS6,

LOAD_START(_Cla1ProgLoadStart),

RUN_START(_Cla1ProgRunStart),

LOAD_SIZE(_Cla1ProgLoadSize),

ALIGN(4)

#endif

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH

#if defined(__TI_EABI__)

GROUP

{

.TI.ramfunc

{

}

ramfuncs

} LOAD = FLASH_BANK0_SEC1,

RUN = RAMGS0GS1

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(4)

#else

.TI.ramfunc : LOAD = FLASH_BANK0_SEC1,

RUN = RAMGS0GS1

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(4)

#endif

.scratchpad : > RAMLS0LS1

.bss_cla : > RAMLS0LS1

controlVariables : > RAMLS0LS1

SFRA_F32_Data : > RAMGS2, ALIGN = 64

SFRA_Data : > RAMGS2, ALIGN = 64

FPUmathTables : > RAMGS3

Cla1DataRam : > RAMLS0LS1

cla_shared : > RAMLS0LS1

CLADataLS1 : > RAMLS0LS1

#if defined(__TI_EABI__)

.const_cla : LOAD = FLASH_BANK0_SEC2_3_4,

RUN = RAMLS0LS1,

RUN_START(Cla1ConstRunStart),

LOAD_START(Cla1ConstLoadStart),

LOAD_SIZE(Cla1ConstLoadSize),

ALIGN(4)

#else

.const_cla : LOAD = FLASH_BANK0_SEC2_3_4,

RUN = RAMLS0LS1,

RUN_START(_Cla1ConstRunStart),

LOAD_START(_Cla1ConstLoadStart),

LOAD_SIZE(_Cla1ConstLoadSize),

ALIGN(4)

#endif

GROUP

{

isrcodefuncs

dclfuncs

} LOAD = FLASH_BANK0_SEC7,

RUN = RAMGS0GS1,

LOAD_START(isrcodefuncsLoadStart),

LOAD_SIZE(isrcodefuncsLoadSize),

LOAD_END(isrcodefuncsLoadEnd),

RUN_START(isrcodefuncsRunStart),

RUN_SIZE(isrcodefuncsRunSize),

RUN_END(isrcodefuncsRunEnd),

// LOAD_START(_isrcodefuncsLoadStart), commented out because of change from COFF to EABI

// LOAD_SIZE(_isrcodefuncsLoadSize),

// LOAD_END(_isrcodefuncsLoadEnd),

// RUN_START(_isrcodefuncsRunStart),

// RUN_SIZE(_isrcodefuncsRunSize),

// RUN_END(_isrcodefuncsRunEnd),

PAGE = 0, ALIGN(4)

// /* CLA specific sections */ //temporally comment out when CLA is not enabled

// Cla1Prog : LOAD = FLASHH,

// RUN = RAMLS2LS3LS4LS5,

// LOAD_START(_Cla1ProgLoadStart),

// RUN_START(_Cla1ProgRunStart),

// LOAD_SIZE(_Cla1ProgLoadSize),

// PAGE = 0, ALIGN(4)

// /* CLA specific sections */ //temporally comment out when CLA is not enabled

// Cla1Prog : LOAD = FLASH_BANK0_SEC7,

// RUN = RAMLS2,

// LOAD_START(Cla1ProgLoadStart),

// RUN_START(Cla1ProgRunStart),

// LOAD_SIZE(Cla1ProgLoadSize),

// PAGE = 0, ALIGN(4)

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

- Mohit

Hi Mohit,

I would suggest using one of the CLA linker cmd files as a starting point and making any needed modifications to that. All the provided F28003x linker cmd files are in the folder path [C2000ware path]/device_support/f28003x/common/cmd/. The linker cmd files with "cla" in the filename already allocate space for the CLA, so it would probably be best to start with the 28003x_cla_flash_lnk.cmd file and seeing if you can get your program working with that.

The only limitation would be that the CLA program must fit in the LSRAM memory allocated for it. For the F28003x, LSRAMs 0-7 are all accessible by the CLA, but they don't necessarily all need to be used. I would try keeping the CLA program allocation just to LSRAM0 and only extending the program to use more LSRAMs if the program can't fit in that section of memory. If the program doesn't fit in the allocated LSRAM memory, it will throw an error when building.

Best Regards,

Delaney