- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Champ,

I am asking for my customer.

They are implementing CRM mode totem pole PFC, the PWM frequency is based on current crossing zero current to determine, which means the EPWM counter resets to zero when CMPSS reaches out to zero (compared value) for CMPSS output is set up, then restart the count in the EPWM counter, then counting up.

Asking on how to trigger EPWM counter reset (counter clears to zero) when CMPSS output is set up on F28003x ?

(1). Is it feasible to do it in hw way on F28003x ? Would the expert explicitly show the configuration of the implementation ?

(2). If not, what is the implementing suggestion here ?

I find an app. note (spracx0) from here, not sure its configuration matches what I need here.

Thanks and regards,

Johnny

Hi Johnny,

Yes that would be possible using the DC Submodule and syncing the time base submodule based on the CMPSS event.

Thanks.

Hi Prarthan,

Would you kindly point out what are the registers to use with DC Submodule sync event to sync. the time base submodule, then reset the time base counter ?

I am trying to configure that.

Thanks for the input.

Regards,

Johnny

Hi Johnny,

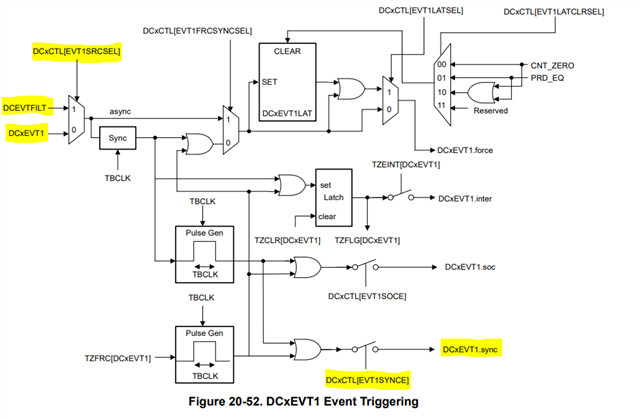

Please see the image and corresponding registers/signals highlighted below

Thanks

Hi Prarthan,

Would you kindly check on is there any problem with below configuration ? Is there any missing ?

EPwmXbarRegs.TRIP4MUX0TO15CFG.bit.MUX0 = 0; // CMPSS1.CTRIPH

EPwmXbarRegs.TRIP4MUXENABLE.bit.MUX0 = 1;

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = 3; // use TRIPIN4 as DCA high input.

EPwm1Regs.TZDCSEL.bit.DCAEVT1 = 1; // DCAH = low, DCAL = don't care.

EPwm1Regs.DCACTL.bit.EVT1SRCSEL = 0; // DCAEVT1 source is DCAEVT1, not filtered signal

EPwm1Regs.DCACTL.bit.EVT1FRCSYNCSEL = 1; // source is passed through asynchronously.

It is set the epwm1.TBPRD to 5khz, and the CMPSS1 input is a 50khz signal.

Now the EPWM1 is still 5k, not sync. with the CMPSS1 output. It is checked that the CMPSS1 is working well.

And CMPSS1Regs.COMPSTS.COMPHSTS can be 1 or 0 according to its input.

Any input or correction on the configuration in bit field ?

Thanks and regards,

Johnny

Hi Johnny,

Are you expecting the TRIP input to be low on trip, high otherwise ?

EPwm1Regs.TZDCSEL.bit.DCAEVT1 = 1; // DCAH = low, DCAL = don't care

Please check our c2000ware example, to see how DC and TZ submodule can be configured and then make the following changes on those so it will be easier to get this working.

Thanks.