- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello, I'm baselining the F28379D MCU's inter-process comms and hit a wall with dual-core RAM configurations. I need some education as to how the CPU2 boot process for RAM works.

I've successfully compiled custom dual-core applications in FLASH configurations, uploaded them via the uniflash command line, and ran them successfully. However, when repeating this process in a RAM configuration, I can't get CPU2 to boot at all.

To achieve a known starting point, I went back to the dual-core blinky example from C2000Ware (driverlib/f2837xd/examples/dual/led) and compiled for a RAM target via CCS. Whether I flash via CCS, the uniflash GUI, or the uniflash command line, I can only get CPU1's LED to blink.

Is there a potential issue with how I am compiling or flashing this example code?

My issue points to a misunderstanding on my part as to how CPU2 boots, so help is appreciated.

uniflash version: v8.7.0

C2000Ware version: v5.02.00.00

CCS version: v12.8.0

OS: Ubuntu 22.04

My uniflash invocation:

flasher=/opt/ti/uniflash_*/dslite.sh

flash_board_config=configs/flash_board_config.ccxml

settings="--verbose -N --config=$flash_board_config"

$flasher $settings --core 2 led_ex1_blinky_cpu2/CPU2_RAM/led_ex1_blinky_cpu2.out

$flasher $settings --core 0 led_ex1_blinky_cpu1/CPU1_RAM/led_ex1_blinky_cpu1.out --run

Executing the following command:

> /opt/ti/uniflash_8.7.0/deskdb/content/TICloudAgent/linux/ccs_base/DebugServer/bin/DSLite flash --verbose -N --config=configs/flash_board_config.ccxml --core 2 led_ex1_blinky_cpu2/CPU2_RAM/led_ex1_blinky_cpu2.out

For more details and examples, please refer to the UniFlash Quick Start guide.

DSLite version 12.7.0.3382

Configuring Debugger (may take a few minutes on first launch)...

Initializing Register Database...

Initializing: IcePick_C_0

Executing Startup Scripts: IcePick_C_0

Initializing: C28xx_CPU1

Executing Startup Scripts: C28xx_CPU1

Initializing: CPU1_CLA1

Executing Startup Scripts: CPU1_CLA1

Initializing: C28xx_CPU2

Executing Startup Scripts: C28xx_CPU2

Initializing: CPU2_CLA1

Executing Startup Scripts: CPU2_CLA1

--- Available Cores ---

0: Texas Instruments XDS100v2 USB Debug Probe/C28xx_CPU1

1: Texas Instruments XDS100v2 USB Debug Probe/CPU1_CLA1

2: Texas Instruments XDS100v2 USB Debug Probe/C28xx_CPU2

3: Texas Instruments XDS100v2 USB Debug Probe/CPU2_CLA1

Connecting...

C28xx_CPU1: GEL Output:

Memory Map Initialization Complete

info: C28xx_CPU1: If erase/program (E/P) operation is being done on one core, the other core should not execute from shared-RAM (SR) as they are used for the E/P code. Also, CPU1 will be halted to determine SR ownership for the CPU which will run the Flash Plugin code, after which CPU1 will be set to run its application. User code execution from SR could commence after both flash banks are programmed.

C28xx_CPU2: GEL Output:

Memory Map Initialization Complete

info: C28xx_CPU2: If erase/program (E/P) operation is being done on one core, the other core should not execute from shared-RAM (SR) as they are used for the E/P code. Also, CPU1 will be halted to determine SR ownership for the CPU which will run the Flash Plugin code, after which CPU1 will be set to run its application. User code execution from SR could commence after both flash banks are programmed.

Loading Program: led_ex1_blinky_cpu2/CPU2_RAM/led_ex1_blinky_cpu2.out

Preparing ...

.text: 0 of 4 at 0x0

.text: 0 of 44 at 0xa2

.text: 0 of 1666 at 0xb000: 2%

Finished: 2%

Setting PC to entry point.: 2%

Success

Executing the following command:

> /opt/ti/uniflash_8.7.0/deskdb/content/TICloudAgent/linux/ccs_base/DebugServer/bin/DSLite flash --verbose -N --config=configs/flash_board_config.ccxml --core 0 led_ex1_blinky_cpu1/CPU1_RAM/led_ex1_blinky_cpu1.out --run

For more details and examples, please refer to the UniFlash Quick Start guide.

DSLite version 12.7.0.3382

Configuring Debugger (may take a few minutes on first launch)...

Initializing Register Database...

Initializing: IcePick_C_0

Executing Startup Scripts: IcePick_C_0

Initializing: C28xx_CPU1

Executing Startup Scripts: C28xx_CPU1

Initializing: CPU1_CLA1

Executing Startup Scripts: CPU1_CLA1

Initializing: C28xx_CPU2

Executing Startup Scripts: C28xx_CPU2

Initializing: CPU2_CLA1

Executing Startup Scripts: CPU2_CLA1

--- Available Cores ---

0: Texas Instruments XDS100v2 USB Debug Probe/C28xx_CPU1

1: Texas Instruments XDS100v2 USB Debug Probe/CPU1_CLA1

2: Texas Instruments XDS100v2 USB Debug Probe/C28xx_CPU2

3: Texas Instruments XDS100v2 USB Debug Probe/CPU2_CLA1

Connecting...

C28xx_CPU1: GEL Output:

Memory Map Initialization Complete

info: C28xx_CPU1: If erase/program (E/P) operation is being done on one core, the other core should not execute from shared-RAM (SR) as they are used for the E/P code. Also, CPU1 will be halted to determine SR ownership for the CPU which will run the Flash Plugin code, after which CPU1 will be set to run its application. User code execution from SR could commence after both flash banks are programmed.

Loading Program: led_ex1_blinky_cpu1/CPU1_RAM/led_ex1_blinky_cpu1.out

Preparing ...

.text: 0 of 4 at 0x0

.text: 0 of 8 at 0x123

.data: 0 of 36 at 0x128

.text: 0 of 1832 at 0x8000

.data: 0 of 764 at 0xa800: 27%

.text: 0 of 4096 at 0xb000: 39%

Finished: 39%

Setting PC to entry point.: 39%

Running...

Success

Hi Brian,

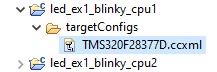

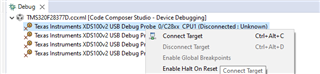

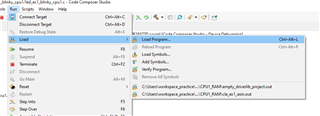

Just to clarify, you are running the led_ex1_blinky_cpu1 and led_ex1_blinky_cpu2 examples unchanged, correct? You should be able to run this example from CCS with the following steps:

Best Regards,

Delaney

Thanks for the response - your steps worked albeit without the two LEDs synced like I expected.

I now just need help transcribing this to the uniflash commandline, my goal is to flash to RAM and immediately run without having to hit the physical restart button on the launchpad. Can you assist with that?

Alternatively, if you can give an example to flash this using the uniflash GUI, I could then transcribe to the commandline myself.

Hi Brian,

I will loop in the Uniflash expert to assist you with this.

Best Regards,

Delaney

Hi Brian,

After the first RAM application has downloaded, have you tried to reset through the command line interface using the "-r" argument?

It's mentioned in the UniFlash Quick Start Guide .

Also, would it be beneficial to your process to generate a package for both CPU1 and CPU2 application prior to calling the DSLite shell?

Thanks and regards,

Charles

Hey Charles, thanks for the reply. I've attempted a number of permutations, including CPU and system resets, swapping which core flashes first, and combinations of the `--run` switch. I'm interpreting your suggestion as:

Fullscreen1234567891011flasher=/opt/ti/uniflash_*/dslite.shflash_board_config=configs/flash_board_config.ccxmlsettings="--verbose -N --config=$flash_board_config"$flasher $settings --core 2 led_ex1_blinky_cpu2/CPU2_RAM/led_ex1_blinky_cpu2.out$flasher $settings -r 0$flasher $settings --core 0 led_ex1_blinky_cpu1/CPU1_RAM/led_ex1_blinky_cpu1.out --runXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXflasher=/opt/ti/uniflash_*/dslite.sh flash_board_config=configs/flash_board_config.ccxml settings="--verbose -N --config=$flash_board_config" $flasher $settings --core 2 led_ex1_blinky_cpu2/CPU2_RAM/led_ex1_blinky_cpu2.out $flasher $settings -r 0 $flasher $settings --core 0 led_ex1_blinky_cpu1/CPU1_RAM/led_ex1_blinky_cpu1.out --run

Is that correct?

In this case, the uniflash execution runs to completion with no errors, but only CPU1 actually boots judging from the state of the LEDs (i.e., the red LED stays on).

I'd attach my ccxml file and binaries for completeness, but looks like I can't attach files to replies. Regardless, the blinky source files were untouched from the C2000Ware example, and were compiled using the default CCS environment.

When you refer to a "package", are you referring to the zip file that uniflash can generate? If so, I don't yet see an advantage over invoking uniflash via my own shell script like I'm currently doing.