Other Parts Discussed in Thread: C2000WARE

Tool/software:

I am unable to configure the EPWMs to load CMPA on a SYNCIN event.

Here is my setup:

I'm using EPWM Modules 1 through 11. I need to load the shadowed CMPA and CMPB value for EPWMs 9 through 11 simultaneously for my design. Right now, I am attempting to do the following

- EPWM 1 configured to generate SYNCOUT pulse when TBCTR=0

- EPWM 2 through 11 configured to use SYNCOUT = SYNCIN

- EPWM 1 through 8 configured to be active high (not complementary)

- EPWM 9 through 11 configured to be active high complementary

- EPWM 9 through 11 configured to load CMPA and CMPB on SYNCIN

This last part is the the one that doesn't seem to work for me.

I have attached a working test project that demonstrates the issue.

The relevant code is in lines 561-577

EPwm9Regs.CMPCTL.bit.LOADAMODE = 0;

EPwm9Regs.CMPCTL.bit.LOADASYNC = 2;

EPwm9Regs.CMPCTL.bit.LOADBMODE = 0;

EPwm9Regs.CMPCTL.bit.LOADBSYNC = 2;

EPwm10Regs.CMPCTL.bit.LOADAMODE = 0;

EPwm10Regs.CMPCTL.bit.LOADASYNC = 2;

EPwm10Regs.CMPCTL.bit.LOADBMODE = 0;

EPwm10Regs.CMPCTL.bit.LOADBSYNC = 2;

EPwm11Regs.CMPCTL.bit.LOADAMODE = 0;

EPwm11Regs.CMPCTL.bit.LOADASYNC = 2;

EPwm11Regs.CMPCTL.bit.LOADBMODE = 0;

EPwm11Regs.CMPCTL.bit.LOADBSYNC = 2;

When I run this program and test whether the PWM duty ratios are updating properly, I see that the duty ratio is never actually loaded, despite the fact that I can confirm the EPWM Sync signal is present.

Here is an image showing the PWM signals, sync signal output on a GPIO pin, and a flag that I'm using for triggering the measurement. The duty ratios should be different before and after the trigger point, but never change.

--------

For comparison, here is the behavior when I set EPwmxRegs.CMPCTL.bit.LOADASYNC = 0 for all three EPWMs. You can see that the duty ratios get updated at the CTR=0 point as they should.

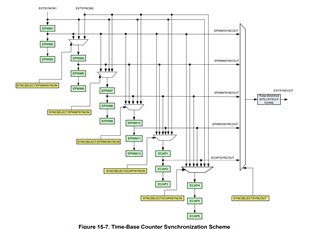

It seems I am missing some setting to get the EPWMs to load on sync, but I am unable to determine what is incorrect here. According to section 15.5 in the Technical Reference Manual I am setting all the CMPCTL registers properly.

Looking forward to hearing from you. I have attached a working project as a .zip file (please be sure to set the value of C2000WARE_ROOT properly in Project Properties > Linked Resources to ensure the library dependencies link properly) (EDIT Nov 22, 2024: project updated in comments)

Regards,

Rahul