Other Parts Discussed in Thread: TMS320F28388D

- Part Number: TMS320F28388D

Tool/software:

Hi Team,

In my current implementation, I have the same two interrupt sources configured for each core:

- CPU1: ADC ISR1, eCAP1

- CPU2: ADC ISR1, eCAP1

Both cores are triggered by the respective ISRs, but the code executed on each core differs. The ePWM module initiates the ADC Start-of-Conversion (SOC), and upon completion of the ADC conversion, ADCINT1 triggers interrupts on both cores. The PWM timer period is approximately 39 µs.

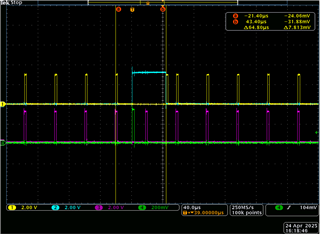

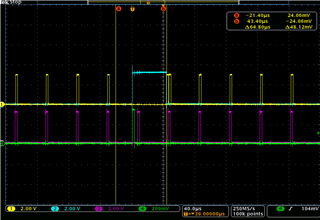

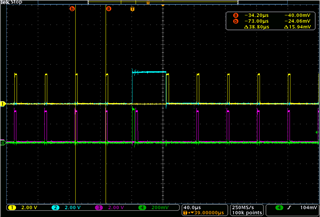

Additionally, once every line cycle, an eCAP interrupt is generated and also triggers both cores. I've captured the interrupt waveforms using GPIOs that toggle at the entry and exit points of each ISR, and the results are shared below.

For testing purposes, I added extra computations inside the eCAP1 ISR that extend beyond the PWM interrupt period.

Waveform Channel Mapping:

- Ch1: CPU1 ADC ISR

- Ch2: CPU1 eCAP ISR

- Ch3: CPU2 ADC ISR

- Ch4: CPU2 eCAP ISR

1.Normally, the ADC ISR is triggered every 39 µs. However, if the eCAP ISR gets serviced before the ADC ISR, the ADC ISR execution is delayed until the eCAP ISR completes.

2.In one scenario, the eCAP ISR completes just before the next ADC ISR, leaving only a small window for ADC ISR execution on CPU1.

3.In another case, the eCAP ISR doesn't leave enough time, resulting in one ADC ISR being skipped. My question is: why did CPU2 also skip the ADC ISR in this scenario?

I suspect that since the ADC peripheral is owned by CPU1, it is responsible for clearing the interrupt flag. If CPU1 does not clear the flag, the ADC ISR won’t trigger again. However, once CPU1 executes the next ADC ISR and clears the flag, CPU2 should be able to respond to the ADC interrupt as well.

My queries are:

- What conditions can lead to both CPU1 and CPU2 missing the ADC ISR under these circumstances?

- Is it possible for a peripheral (like ePWM or ADC) owned by one core to trigger an ISR on the other core without triggering it on its own core, considering the interrupt flag cannot be cleared by the non-owning core?

- Given that the eCAP ISR has the lowest priority, is it a valid approach to use simple nesting (enabling/disabling interrupts using

EINTandDINT like below) inside the eCAP ISR to ensure the ADC ISR always gets executed?

__interrupt void ecap3ISR(void)

{

if (ECap3Regs.ECFLG.bit.CEVT1 == 0x1)

{

ECap3Regs.ECCLR.bit.CEVT1 = 0x1;

}

if (ECap3Regs.ECFLG.bit.CEVT2 == 0x1)

{

ECap3Regs.ECCLR.bit.CEVT2 = 0x1;

}

if (ECap3Regs.ECFLG.bit.CEVT3 == 0x1)

{

ECap3Regs.ECCLR.bit.CEVT3 = 0x1;

}

if (ECap3Regs.ECFLG.bit.CEVT4 == 0x1)

{

ECap3Regs.ECCLR.bit.CEVT4 = 0x1;

}

PieCtrlRegs.PIEACK.all = PIEACK_GROUP4;

ECap3Regs.ECCLR.bit.INT = 0x1;

EINT;

/* some code

*/

DINT;

}

4. One final question on interrupt nesting: If I want an ePWM interrupt to preempt an eCAP ISR (from a different interrupt group), what are the steps to enable that? TI’s documentation covers nesting within the same group, but not across groups.

Are there risks in allowing eCAP to be nested by ePWM? I want to avoid a scenario like eCAP1 -> EINT -> eCAP2 -> EINT -> ePWM, where two eCAP ISRs delay the higher-priority ePWM ISR. My goal is to minimize latency and ensure ePWM isn't delayed by back-to-back eCAPs.