Other Parts Discussed in Thread: F28M36P63C2, C2000WARE

Hello,

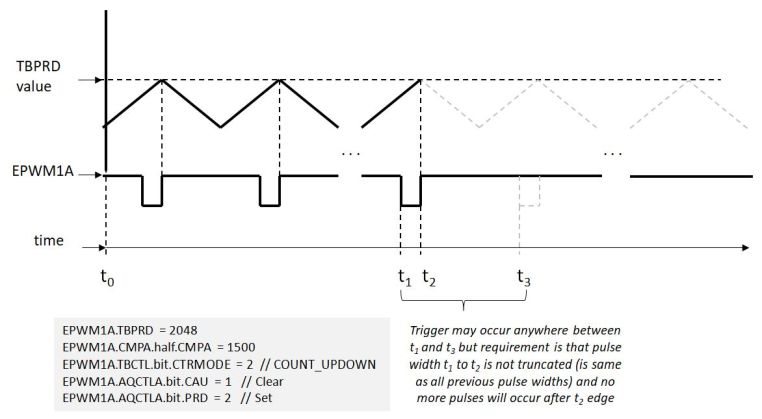

I am trying to understand how to halt the repetition of an EPWMx pulse train output, such that the last pulse is not truncated. The figure below illustrates the situation. I'd prefer to use a software command to initiate the halting, such as EPWM1.AQCSFRC.bit.CSFA = 2, which would place the output to a continuous high value, which is what I want. However, I want the final negative-going pulse to be like all those before it. In my case, the document sprug04a.pdf applies, and I have studied all the submodules including Dead Band and Trip Zone, but all I can gather from this document is that if the software forcing (CSFA=2) command happens to occur during the negative-going pulse, the pulse width will be truncated accordingly, that is, the forcing action is completely asynchronous to EPWM1 signal. I searched the community threads on E2E and some of the topics come close to what I am trying to do, but nothing seems conclusive that this is possible. I am just beginning to use ePWM modules, so perhaps I am missing something. I would greatly appreciate any suggestions.

Thanks,

Nick