Other Parts Discussed in Thread: C2000WARE,

Tool/software: Code Composer Studio

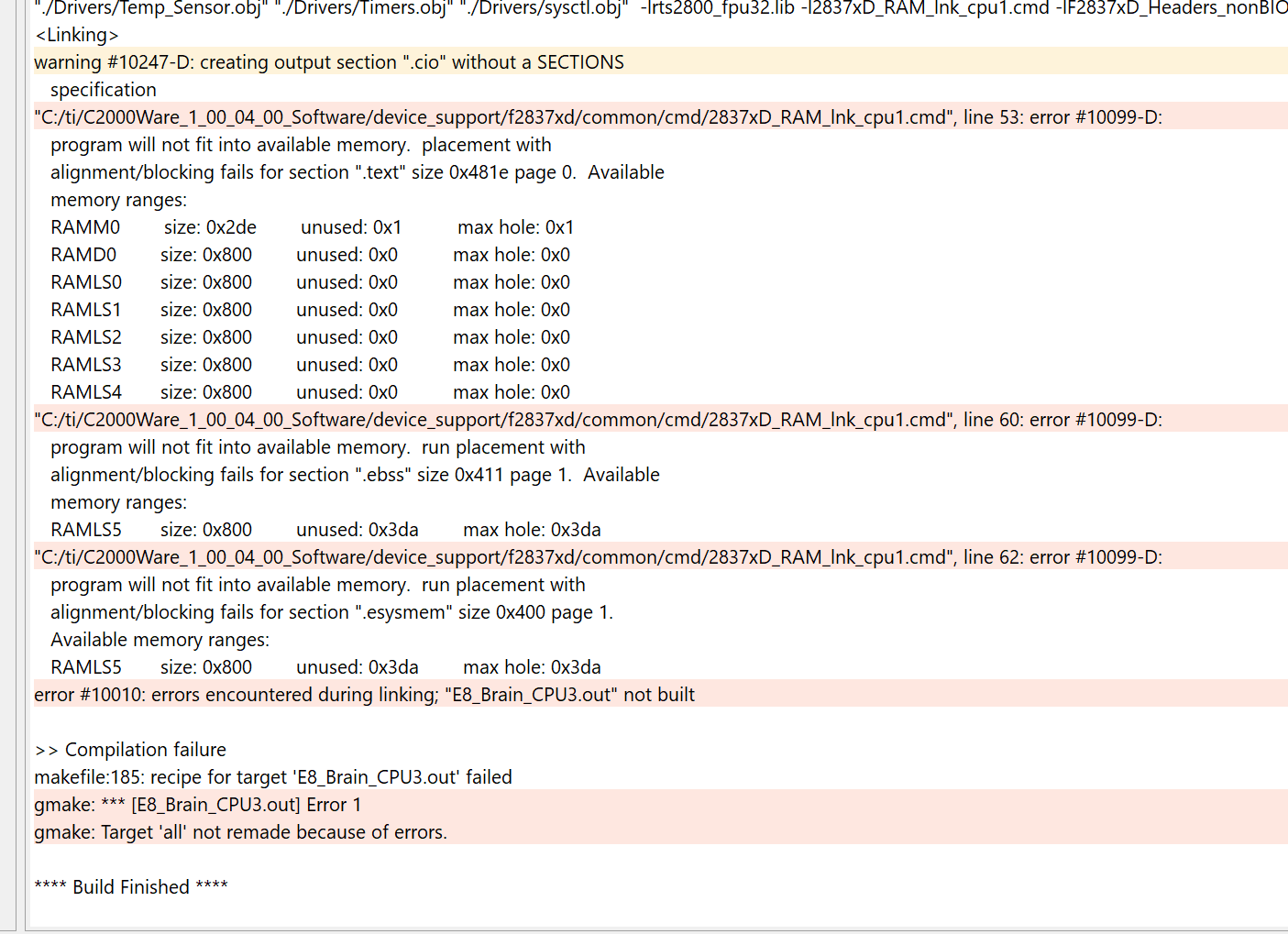

I am getting the following error when trying to get a dual core application into the MCU.

Can anybody help me understand how to get this working. I did the blinky dual core example project and that went fine but I am unable to get my project to do the same thing.

The error indicates "No core matches the pattern 'CPU1'. Is there something that CPU1 must be running before CPU2 can be downloaded? I found another

post that asked the same question and I tried the suggested solution which worked for the original poster but it does not work in my case.

C28xx_CPU2: GEL Output:

Memory Map Initialization Complete

C28xx_CPU2: If erase/program (E/P) operation is being done on one core, the other core should not execute from shared-RAM (SR) as they are used for the E/P code. Also, CPU1 will be halted to determine SR ownership for the CPU which will run the Flash Plugin code, after which CPU1 will be set to run its application. User code execution from SR could commence after both flash banks are programmed.

C28xx_CPU2: Error occurred during flash operation: No core matches the pattern 'CPU1'

C28xx_CPU2: Error setting the GSxMSEL register for Flash operations

C28xx_CPU2: Error occurred during flash operation: Timed out waiting for target to halt while executing wr_pll.alg

C28xx_CPU2: Error writing the PLL values (Flash algorithm timed out). Operation cancelled.

C28xx_CPU2: Perform a debugger reset and execute the Boot-ROM code (click on the RESUME button in CCS debug window) before erasing/loading the Flash. If that does not help to perform a successful Flash erase/load, check the Reset cause (RESC) register, NMI shadow flag (NMISHDFLG) register and the Boot-ROM status register for further debug.

C28xx_CPU2: Error occurred during flash operation: No core matches the pattern 'CPU1'

C28xx_CPU2: File Loader: Memory write failed: Unknown error

C28xx_CPU2: GEL: File: C:\Users\Dave\workspace_v8\E8_Brain_CPU3\CPU2_FLASH_DEBUG\E8_Brain_CPU3.out: Load failed.

C28xx_CPU2: Error occurred during flash operation: No core matches the pattern 'CPU1'

C28xx_CPU2: Error setting the GSxMSEL register for Flash operations

C28xx_CPU2: Error occurred during flash operation: Timed out waiting for target to halt while executing pwrite_en.alg

C28xx_CPU2: Flash operation timed out waiting for the algorithm to complete. Operation cancelled.

C28xx_CPU2: Perform a debugger reset and execute the Boot-ROM code (click on the RESUME button in CCS debug window) before erasing/loading the Flash. If that does not help to perform a successful Flash erase/load, check the Reset cause (RESC) register, NMI shadow flag (NMISHDFLG) register and the Boot-ROM status register for further debug.

C28xx_CPU2: Error occurred during flash operation: No core matches the pattern 'CPU1'

C28xx_CPU2: Error occurred during flash operation: No core matches the pattern 'CPU1'

C28xx_CPU2: Error setting the GSxMSEL register for Flash operations