Other Parts Discussed in Thread: LMH6715

Hi

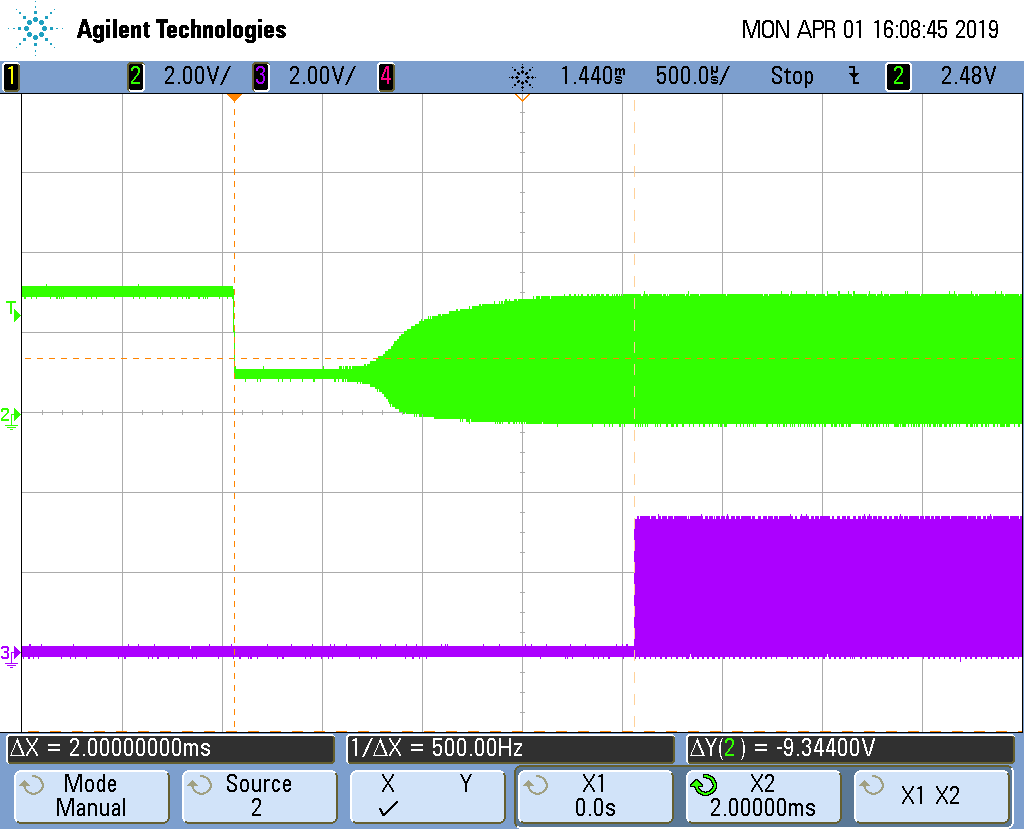

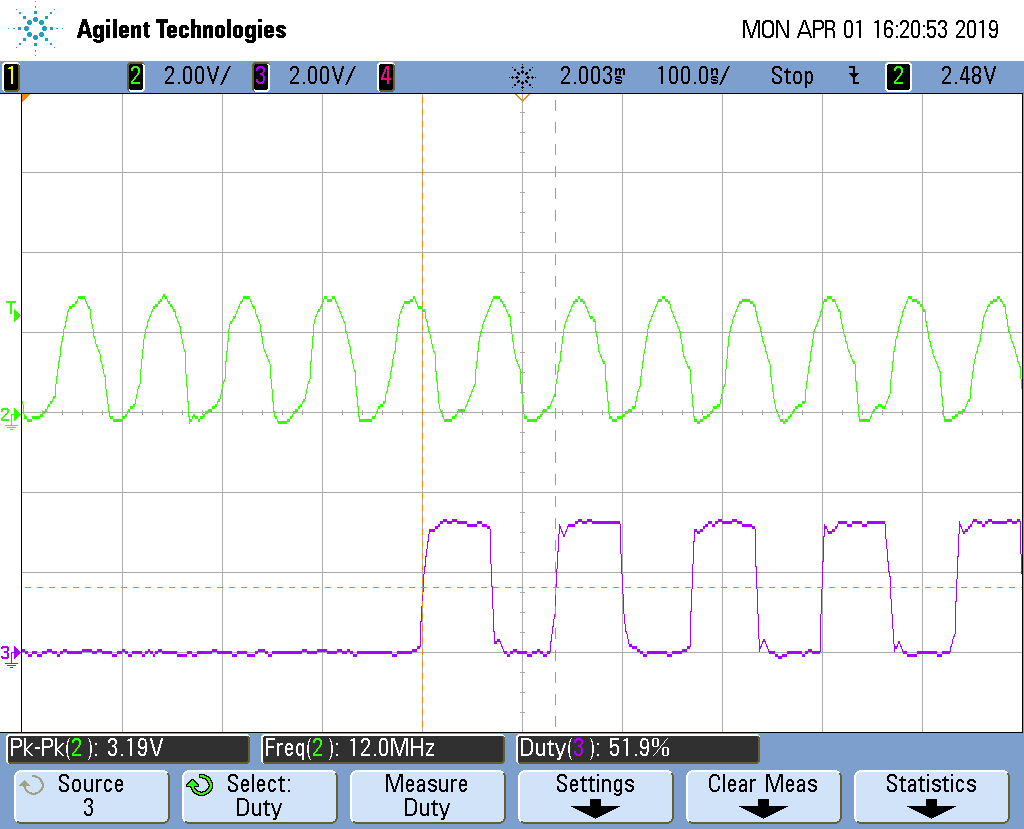

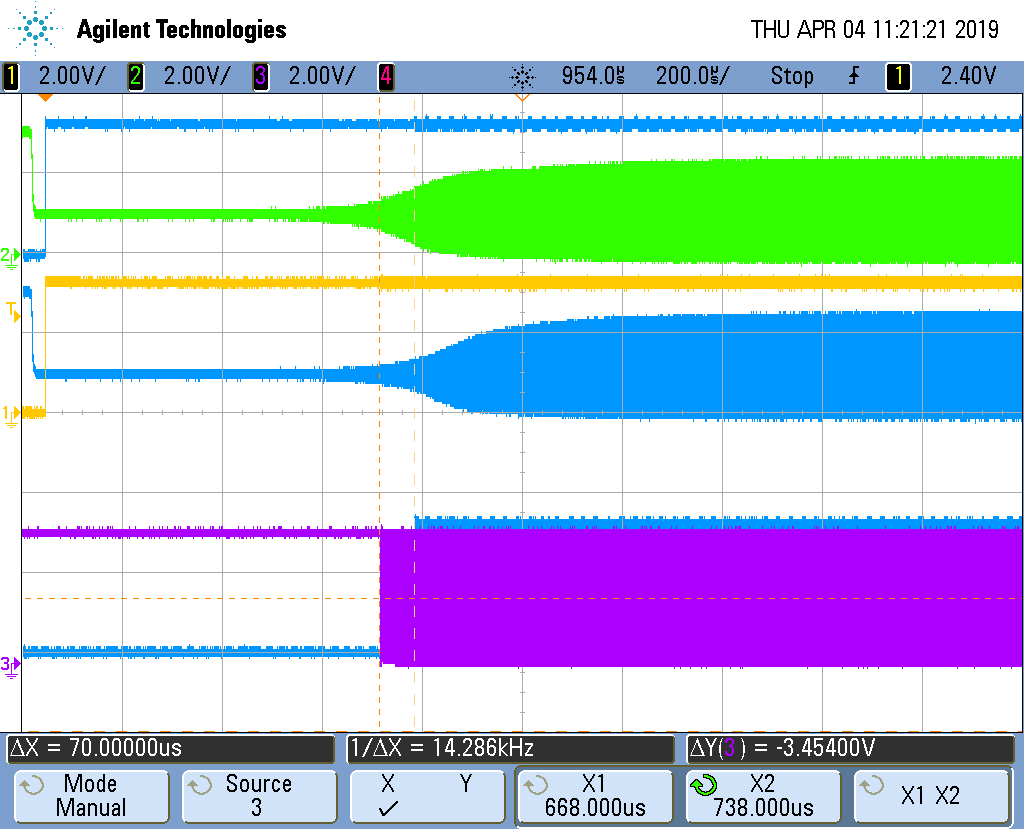

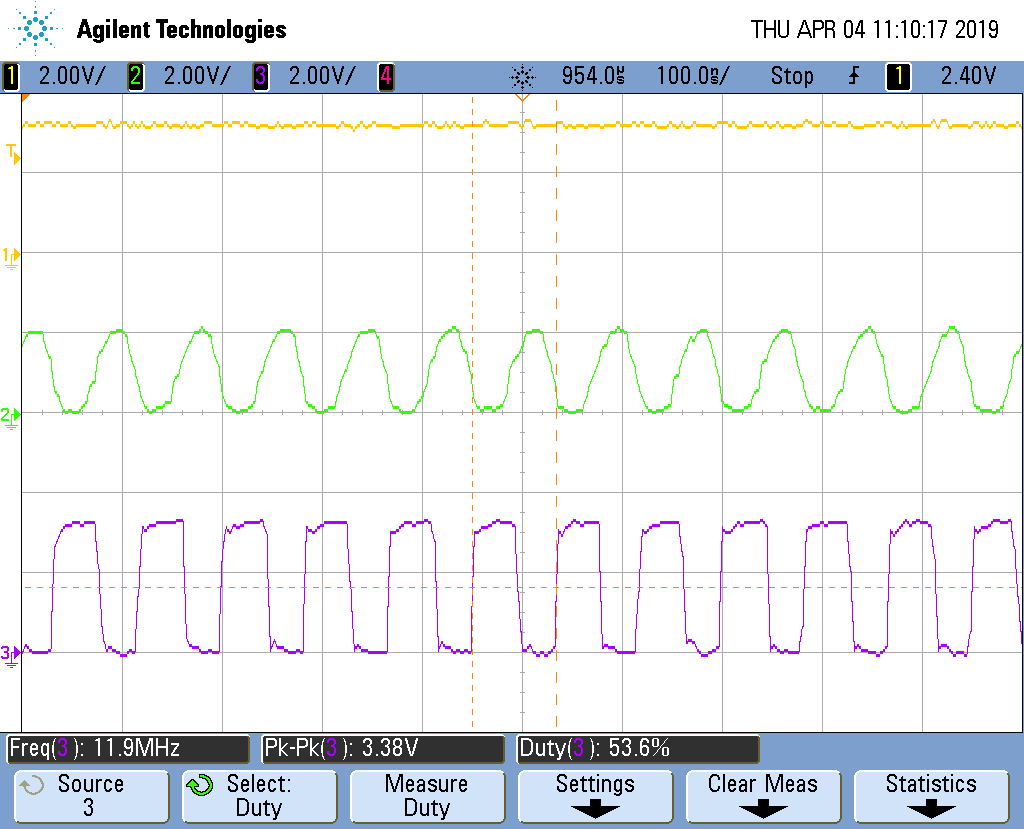

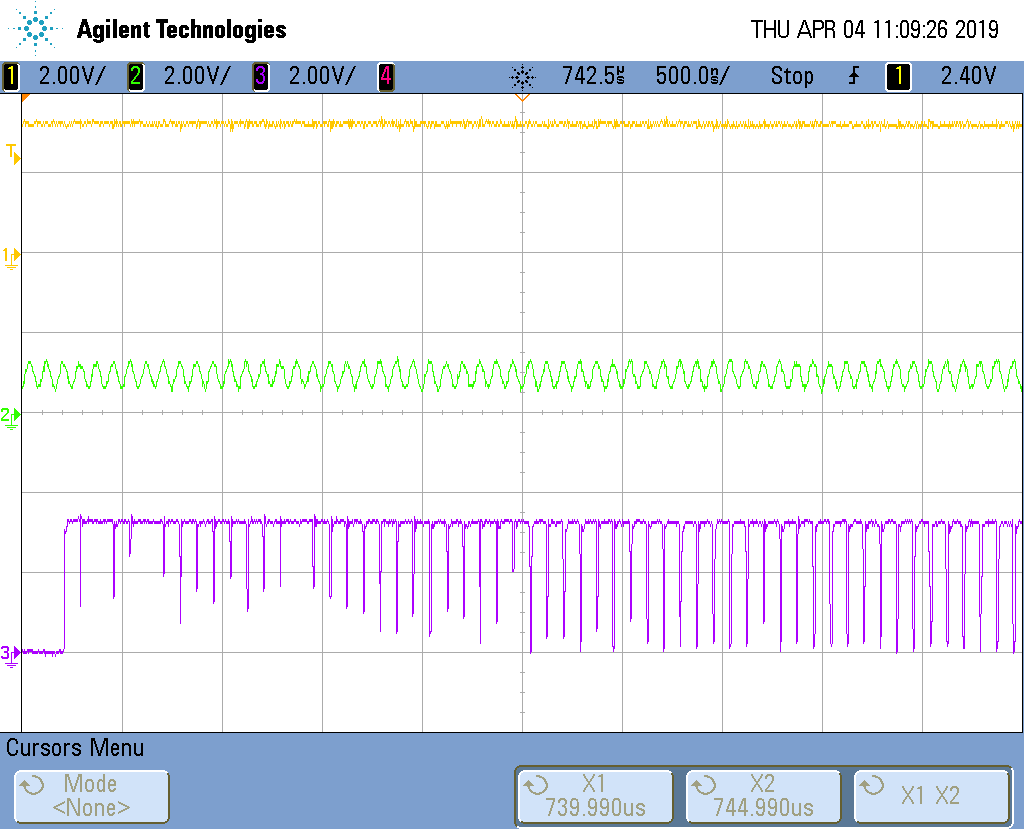

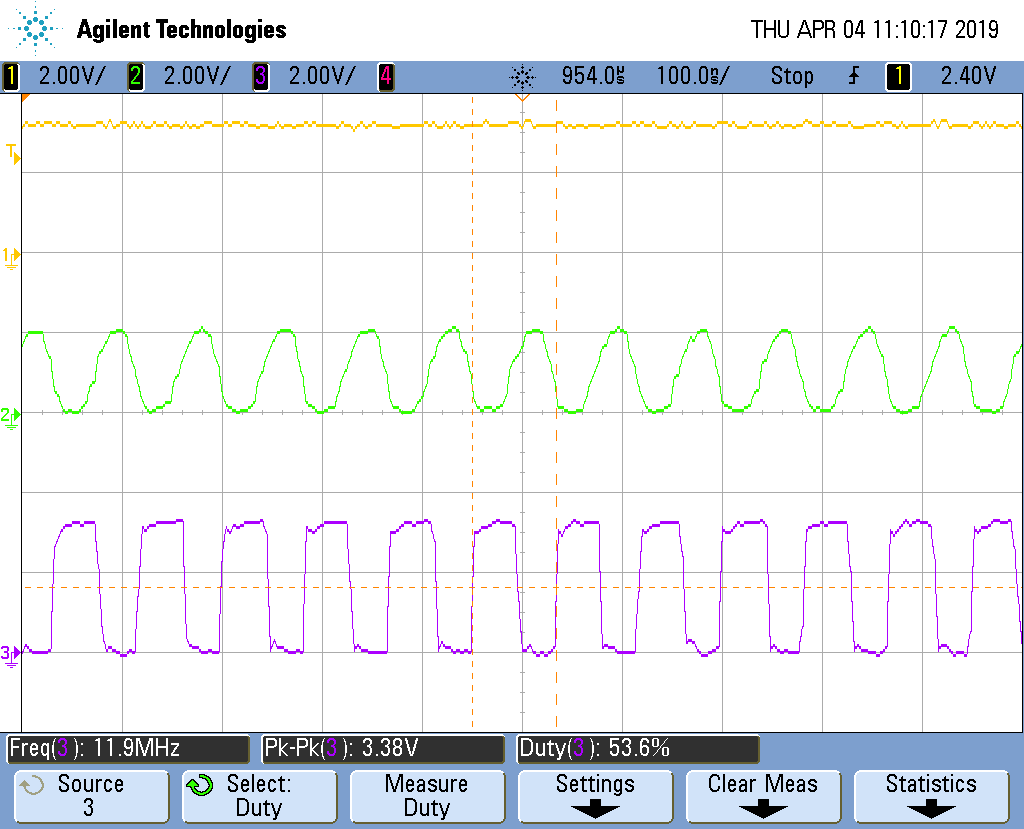

I have been measuring the crystal signals on the 28069 microcontroller board we use. The main thing is to make sure the crystal is not overdriven (or under driven) and has enough gain margin to reliably start given tolerances and temperature extremes. As we will be moving to the 280049 I thought I would measure the 280049 launchpad crystal oscillator. As I do not have an expensive current probe or FET voltage probe I built a unity gain wideband buffer amplifier with 2pF input capacitance. I measure 3.16Vpp (Peak to Peak) with of course a DC offset. This seems consistent with the spec for the 280049, whose oscillator voltage is more than the 1.8V specified for the 28069.

The ESC-200-18-30B crystal is specified for 20MHz 18pF 40ohm 100uW max.

If you use a formula quoted by ST in an Oscillator Design Guide from them, one can estimate the crystal drive power from the voltage.

Pd = Irms^2 * ESR

Irms = 2 pi F * Ct * Vpp/(2 *sqrt(2))

Ct = C1 + (Cstray/2) + Cprobe = 15pF + ? + 2pF. Assuming about Cstray = 4pF (pin input capacitance + PCB capacitance) then Ct = 19pF.

This then gives Pd = 2.66mA ^2 * 40 = 284uW and the crystal is specified for 100uW max.

OK, its a development board and 40ohm is ESR max. So no big deal?! I have also had some pre-production boards with 200uW in a different 100uW max. crystal and no problems short term. However, the same crystal size from another manufacturer states Pd max as 300uW. I am not a crystal expert and do not know what the statistical difference between max. ESR and typical likely is. I also cannot vouch for the above formula, but I have used it and compared the result to a current measurement of a crystal at 12MHz (see later on the probe I used) and the results were comparable.

The point really is TI provides little information in general on crystal oscillator design. The statement in the data-sheets is :

"TI recommends that the crystal manufacturer characterize the crystal with the application board" - not much help really.

There is no information for instance on the oscillator transconductance - a figure useful in calculating likely gain margins before embarking on measurements. If you take the development board design then you may have problems later in the field - or maybe not.

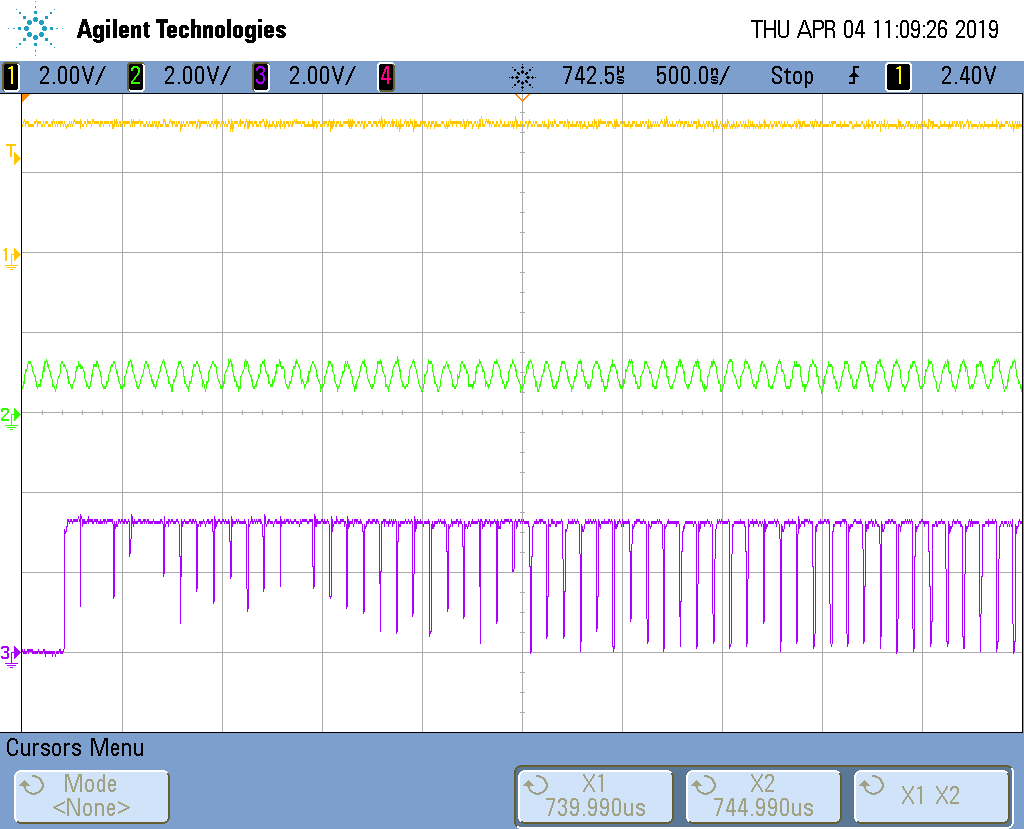

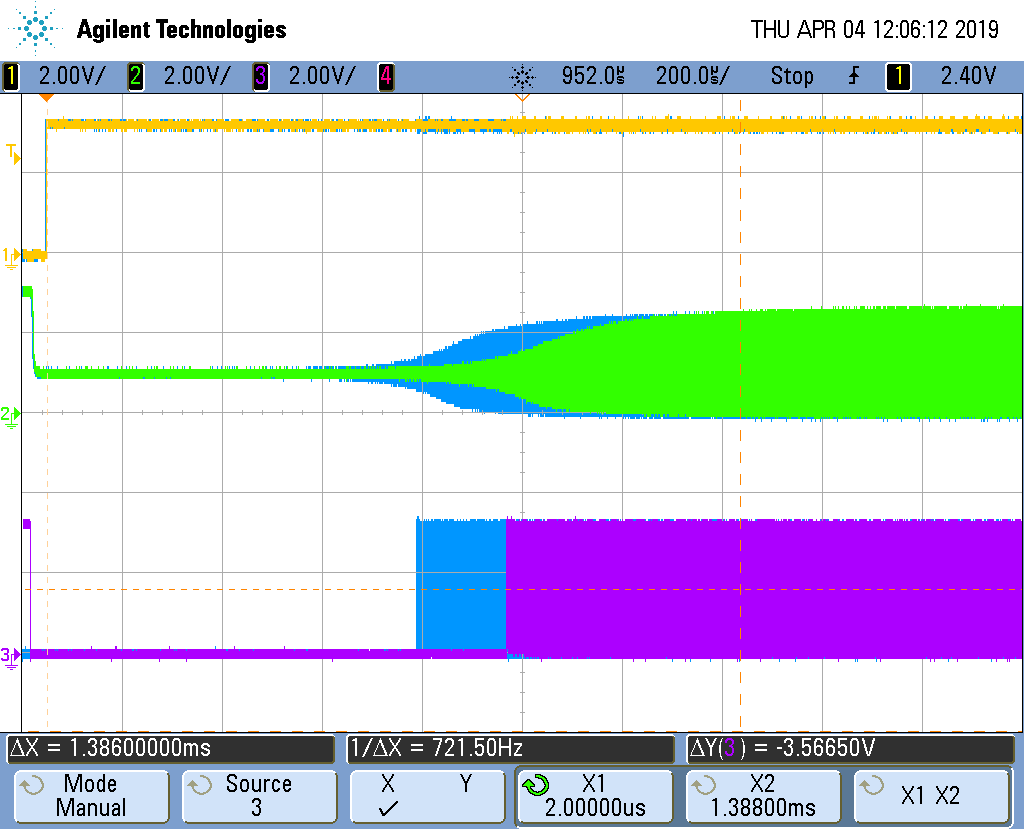

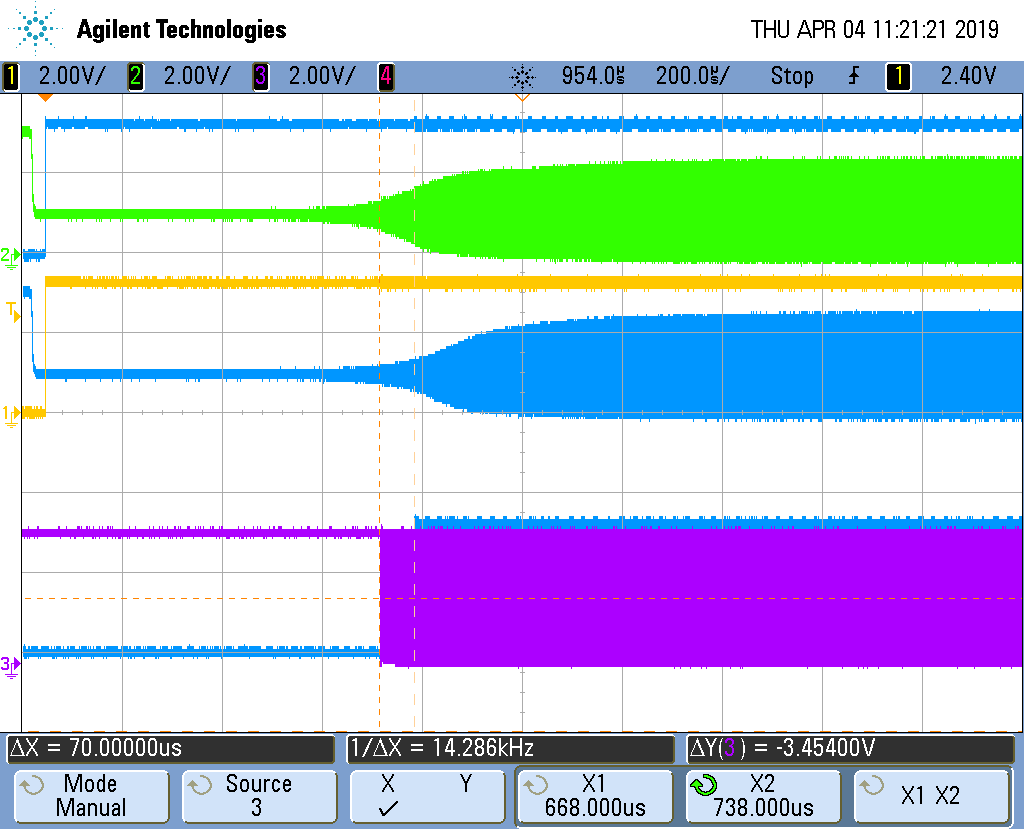

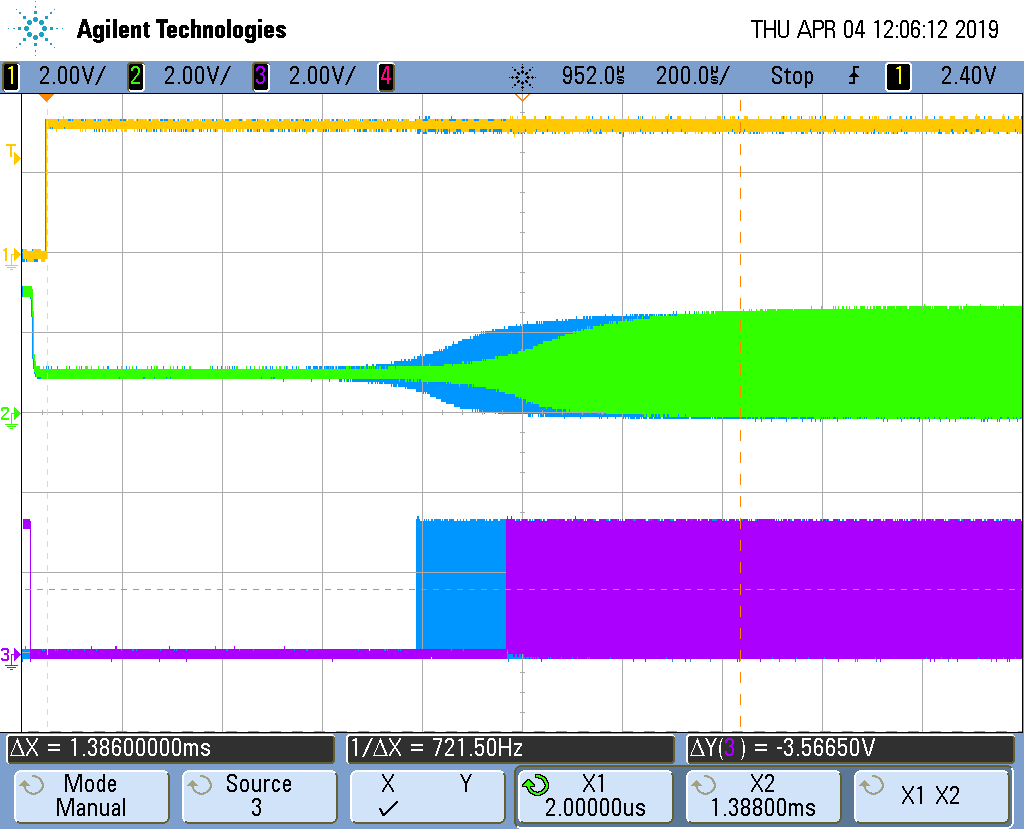

If you want to measure the current in the crystal without an expensive current probe I have also done the following to measure 10-12MHz crystals:

39turns on a 4C65 TN10/6/4 NiZn ferrite core terminated with 390ohms (10mV/mA). Pass some thin coax through the core as primary and connect in series with the crystal - all leads short as possible. Ground one end of the shield to the oscillator / micro ground. You then need 2 or more stages of wide bandwidth opamps with gain 3 - 4 each. I used two AD8039 amplifiers with gain each 4, but a current feedback type say LMH6715 may be better. Apply HF layout see Jim Williams'

Output the amplifier though 50ohms and terminate with 50ohms on the scope. I calibrated the probe by measuring the current output of a Keysight function generator with its 50ohm output shorted. Alternatively use a higher resistor value i.e., 1K and set to 2Vpp to get 2Vpp/1050ohms = 1.9mApp. Leads short as possible!

Finally, I know I make mistakes (believe me!) so don't accept what I have said as read - try to measure the crystal oscillator yourself and make your own conclusion. I hope in future TI will lend a bit more support to the topic.

Cheers