Hi expert,

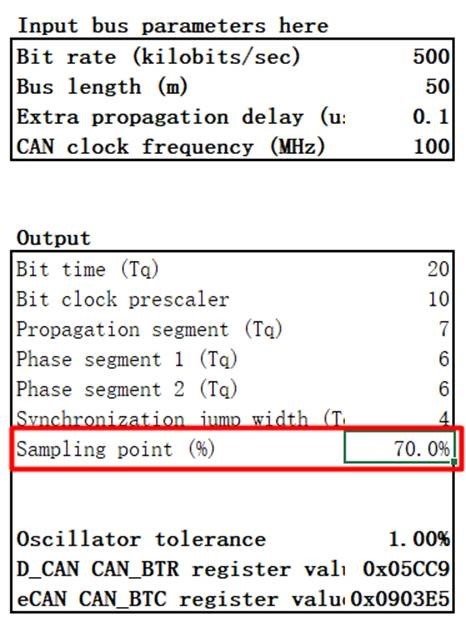

My customer is configurationg CAN on 100M F280049 device. There targeting baurd rate is 500k/bits.

They get bit timing configuration from excel calculation sheet, result shown below:

Tseg1 = 13

Tseg2 = 6

SJW = 4

BPR = 10

Oscillator tolerance: df = 1.00%

They also worked out another set of configuration:

Tseg1 = 5

Tseg2 = 4

SJW = 2

BPR = 20

Oscillator tolerance: df = 1.587%

May I know if it will make a difference between these two?

How could I understand a Oscillator tolerance? How do I know how much it should be? (smaller the better?)

BTW, what is sampling rate here?

Thanks

Sheldon