- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I have big problem in my project.

I am writing a code on TMS320F280025C for my own buck converter with reference to C2000 Digital Power Buck Converter BoosterPack. It runs very well. I am going to implement PLC communication using TI PLC IC AFE031 and use it reference code from TIDA-60001 as reference. I need to include files fsk_corr_detect.lib, fsk_corr_detector.h and fsk_packetization.h in my main program.

I copied these files under my project directory and added below code in my main project

#include <buck.h>

#include "fsk_corr_detector.h"

#include "fsk_packetization.h"

However, I got a warning message below

warning #10373-D: library "../fsk_corr_detect.lib" contains TI-COFF object files which are incompatible with the ELF output file. Ensure you are using the proper library.

warning #10373-D: library "../fsk_corr_detect.lib" contains TI-COFF object files which are incompatible with the ELF output file. Ensure you are using the proper library.

Please advise how to fix it.

BR

HK Woo

HK,

Thanks for reaching out to the E2E forum. I understand that you need the FSK lib in EABI format, correct? Let me check with the code author to determine when we can get a EABI compatible LIB to share with you. I will reply back tomorrow on the status.

Best,

Matthew

I'm going to ask for the LIB to be recompiled into EABI format. I'll let you know a timetable by tomm.

Best,

Matthew

Hi Mattew,

I am very appreciate your help. Be franked to you, I need to have the EABI lib as soon as possible. It affects our sample delivery schedule.

We are still working to understand the issues of converting this from COFF to EABI, and if there is testing that needs to be done to verify the new compilation works correctly.

Best,

Matthew

Hung,

Please try the attached, this is compiled for EABI. I think there are some additional optimizations that can be had, but wanted to let you try this first.

Best,

Matthewfsk_corr_detect_eabi.lib

Hi Matthew

Sorry for late replay since it was national holiday I had tried to test the attached lib. Please find my test result.

1. I added below and copied the lib to my project directory and complied it. It is no error message

#include "fsk_packetization.h"

#include "fsk_corr_detector.h"

2. With item 1 configuration and added HAL_afe031_rxEnable(); to my main.c

Have an error message as below

"../device/28002x_generic_flash_lnk.cmd", line 78: warning #10068-D: no matching section

undefined first referenced

symbol in file

--------- ----------------

HAL_afe031_rxEnable ./buck_main.obj

error #10234-D: unresolved symbols remain

error #10010: errors encountered during linking; "Mercury_Buck.out" not built

gmake[1]: *** [Mercury_Buck.out] Error 1

gmake: *** [all] Error 2

makefile:167: recipe for target 'all' fail

and then configure property of project Property -> CCS Build -> C2000 Linker -> File Search Path and then add the file "fsk_corr_detect.lib" (I renamed your provided file). Still got the error message

Hung,

Please look at the boostxl_afe031_f28004x_rx project in C2000 Ware C:\ti\c2000\C2000Ware_3_04_00_00\device_support\f28004x\examples\boostxl_afe031_f28004x_rx, as there are additional includes like afe031_config.h and hal_afe031.h that need to be added. Your local project will need to include those as well.

Best,

Matthew

Hi Matthew

I still get an error as below

**** Build of configuration RELEASE for project Mercury_Buck ****

"C:\\ti\\ccs1011\\ccs\\utils\\bin\\gmake" -k -j 8 all -O

Building file: "../buck_main.c"

Invoking: C2000 Compiler

"C:/ti/ccs1011/ccs/tools/compiler/ti-cgt-c2000_20.2.4.LTS/bin/cl2000" -v28 -ml -mt --float_support=fpu32 --idiv_support=idiv0 --tmu_support=tmu0 -O3 --opt_for_speed=5 --fp_mode=relaxed --include_path="C:/ti/c2000/C2000Ware_3_04_00_00/libraries/math/IQmath/c28/include" --include_path="C:/ti/c2000/C2000Ware_3_04_00_00" --include_path="C:/ti/c2000/C2000Ware_3_04_00_00/driverlib/f28002x/driverlib" --include_path="C:/ti/c2000/C2000Ware_3_04_00_00/device_support/f28002x/common/include" --include_path="C:/ti/c2000/C2000Ware_3_04_00_00/device_support/f28002x/headers/include" --include_path="C:/Users/hkwoo/workspace_v10/Mercury_Buck" --include_path="C:/Users/hkwoo/workspace_v10/Mercury_Buck/device" --include_path="C:/Users/hkwoo/workspace_v10/Mercury_Buck/libraries/sfra" --include_path="C:/Users/hkwoo/workspace_v10/Mercury_Buck/libraries/DCL" --include_path="C:/Users/hkwoo/workspace_v10/Mercury_Buck/libraries/SFO" --include_path="C:/ti/ccs1011/ccs/tools/compiler/ti-cgt-c2000_20.2.4.LTS/include" --advice:performance=all --define=_TI_EABI_ --define=_DEBUG --define=F28x_DEVICE --define=CPU1 --define=LARGE_MODEL --define=_FLASH --define=BUCK_CONTROL_RUNNING_ON_CPU -g --float_operations_allowed=32 --diag_suppress=10063 --diag_suppress=173 --diag_warning=225 --diag_wrap=off --display_error_number --quiet --gen_func_subsections=on --abi=eabi --cla_signed_compare_workaround=on -k --asm_listing --preproc_with_compile --preproc_dependency="buck_main.d_raw" --include_path="C:/Users/hkwoo/workspace_v10/Mercury_Buck/RELEASE/syscfg" "../buck_main.c"

>> Compilation failure

subdir_rules.mk:9: recipe for target 'buck_main.obj' failed

"C:\ti\c2000\C2000Ware_3_04_00_00\device_support\f28002x\headers\include\f28002x_lin.h", line 238: error #41: expected an identifier

"C:\ti\c2000\C2000Ware_3_04_00_00\device_support\f28002x\headers\include\f28002x_lin.h", line 238: error #80: expected a type specifier

"C:\ti\c2000\C2000Ware_3_04_00_00\device_support\f28002x\headers\include\f28002x_lin.h", line 238: error #170: a function type is not allowed here

"C:\ti\c2000\C2000Ware_3_04_00_00\device_support\f28002x\headers\include\f28002x_lin.h", line 238: warning #109-D: signed bit field of length 1

"C:\ti\c2000\C2000Ware_3_04_00_00\device_support\f28002x\common\include\f28002x_globalprototypes.h", line 92: error #41: expected an identifier

"C:\ti\c2000\C2000Ware_3_04_00_00\device_support\f28002x\common\include\f28002x_globalprototypes.h", line 92: error #80: expected a type specifier

"C:\ti\c2000\C2000Ware_3_04_00_00\device_support\f28002x\common\include\f28002x_globalprototypes.h", line 92: error #91: function returning function is not allowed

"../buck_main.c", line 83: warning #179-D: variable "dummy_counter" was declared but never referenced

6 errors detected in the compilation of "../buck_main.c".

Could you help me to fix it?

Thanks

Hung,

Sorry for the delay in replying, I'm not sure why the compiler would be throwing these errors since line 41 is the first line of code in each file, basically an #ifndef statement. I need to check with some others if they have seen this before.

Best,

Matthew

Hung,

I think that there is co-mingling of driverLIB and bitfield type styles going on. Was there a base project in C2000Ware that you started with to make your current project?

Perhaps a basic question, but are you using the LIN module in your system?

Best,

Matthew

Hi Matthew

I still found problem during compiling with below message

**** Build of configuration RELEASE for project Mercury_Buck ****

"C:\\ti\\ccs1011\\ccs\\utils\\bin\\gmake" -k -j 8 all -O

Building target: "Mercury_Buck.out"

Invoking: C2000 Linker

"C:/ti/ccs1011/ccs/tools/compiler/ti-cgt-c2000_20.2.4.LTS/bin/cl2000" -v28 -ml -mt --float_support=fpu32 --idiv_support=idiv0 --tmu_support=tmu0 -O3 --opt_for_speed=5 --fp_mode=relaxed --advice:performance=all --define=_TI_EABI_ --define=_DEBUG --define=F28x_DEVICE --define=CPU1 --define=LARGE_MODEL --define=_FLASH --define=BUCK_CONTROL_RUNNING_ON_CPU -g --float_operations_allowed=32 --diag_suppress=10063 --diag_suppress=173 --diag_warning=225 --diag_wrap=off --display_error_number --quiet --gen_func_subsections=on --abi=eabi --cla_signed_compare_workaround=on -k --asm_listing -z -m"Mercury_Buck.map" --heap_size=0x100 --stack_size=0x200 --warn_sections -i"C:/ti/ccs1011/ccs/tools/compiler/ti-cgt-c2000_20.2.4.LTS/lib" -i"C:/Users/hkwoo/workspace_v10/Mercury_Buck/libraries/sfra" -i"C:/Users/hkwoo/workspace_v10/Mercury_Buck/libraries/FPUfastRTS" -i"C:/Users/hkwoo/workspace_v10/Mercury_Buck/device/driverlib" -i"C:/Users/hkwoo/workspace_v10/Mercury_Buck/libraries/SFO" -i"C:/ti/ccs1011/ccs/tools/compiler/ti-cgt-c2000_20.2.4.LTS/include" --reread_libs --diag_wrap=off --display_error_number --xml_link_info="Mercury_Buck_linkInfo.xml" --entry_point=code_start --rom_model -o "Mercury_Buck.out" "./buck.obj" "./buck_hal.obj" "./buck_main.obj" "./buck_user.obj" "./device/device.obj" "./device/f28002x_codestartbranch.obj" "./libraries/DCL/DCL_error.obj" "./libraries/sfra/sfra_gui_scicomms_driverlib.obj" "../fsk_corr_detect.lib" "../device/28002x_generic_flash_lnk.cmd" "../device/driverlib/driverlib.lib" "../libraries/FPUfastRTS/rts2800_fpu32_fast_supplement_eabi.lib" "../libraries/SFO/SFO_v8_fpu_lib_build_c28_driverlib_eabi.lib" "../libraries/sfra/sfra_f32_tmu_eabi.lib" -ldriverlib.lib -lsfra_f32_tmu_eabi.lib -lrts2800_fpu32_fast_supplement_eabi.lib -lrts2800_fpu32_eabi.lib -lSFO_v8_fpu_lib_build_c28_driverlib_eabi.lib -llibc.a

>> Compilation failure

makefile:170: recipe for target 'Mercury_Buck.out' failed

"../device/28002x_generic_flash_lnk.cmd", line 78: warning #10068-D: no matching section

undefined first referenced

symbol in file

--------- ----------------

FSK_CORR_DETECTOR_RUN ./buck_main.obj

error #10234-D: unresolved symbols remain

error #10010: errors encountered during linking; "Mercury_Buck.out" not built

gmake[1]: *** [Mercury_Buck.out] Error 1

makefile:166: recipe for target 'all' failed

gmake: *** [all] Error 2

**** Build Finished ****

FSK_CORR_DETECTOR_RUN function can't been found.

I have added these header files and fsk_corr_detect.lib to root of project.

#include <buck.h>

#include <fsk_corr_detector.h>

#include <fsk_packetization.h>

Please advise how to fix it.

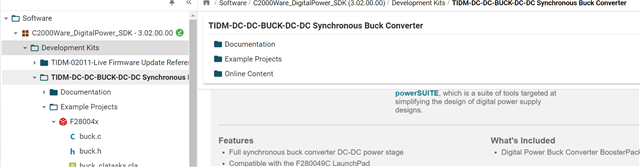

Regarding to your question. My current project is using TI Digital BUCK Convertor. Please refer to below screen capture.

Hung,

I see the same issue when I add the EABI.lib to my RX project. I need to pull in some others, I'm not sure why the archiver is building the LIB without errors if this function is not defined properly(I see the function in the source files).

Best,

Matthew

Hung,

I think I resolved it, there looks to be a different output for assembly functions from COFF to EABI(I need to look into this a bit more). Please try the attached(you can re-name as needed).

Best,

Matthewfsk_corr_detect_lib_eabi.lib

It is ok. However, I will have some question about how to convert the demo code to my project. For example, I would like to use below code in my project.

uint16_t TempPIEIER;

TempPIEIER = PieCtrlRegs.PIEIER2.all;

IER |= M_INT1;

IER &= MINT1; // Set "global" priority

PieCtrlRegs.PIEIER2.all &= MG1_1; // Set "group" priority

PieCtrlRegs.PIEACK.all = 0xFFFF; // Enable PIE interrupts

asm(" NOP"); // Wait one cycle

EINT;

However, it always prompts "PieCtrlRegs" is undefined. Please advise how to use it

Hi Matthew

Bad news, it is found that the lib still has problems. I found below error as I write a code for 586Hz ISR found

undefined first referenced

symbol in file

--------- ----------------

EPWM_clearInterruptStatus ./buck_main.obj

markCosineSum ../fsk_corr_detect_lib_eabi.lib<fsk_corr_bitrate_run.obj>

markSineSum ../fsk_corr_detect_lib_eabi.lib<fsk_corr_bitrate_run.obj>

markSumSquared ../fsk_corr_detect_lib_eabi.lib<fsk_corr_bitrate_run.obj>

spaceCosineSum ../fsk_corr_detect_lib_eabi.lib<fsk_corr_bitrate_run.obj>

spaceSineSum ../fsk_corr_detect_lib_eabi.lib<fsk_corr_bitrate_run.obj>

spaceSumSquared ../fsk_corr_detect_lib_eabi.lib<fsk_corr_bitrate_run.obj>

My code is below :

#pragma CODE_SECTION(BIT_DETECT_ISR,".TI.ramfunc");

__interrupt void BIT_DETECT_ISR(void)

{

EALLOW;

//

// Enable ADC ISR Nesting

//

/*

uint16_t TempPIEIER;

TempPIEIER = PieCtrlRegs.PIEIER2.all;

IER |= M_INT1;

IER &= MINT1; // Set "global" priority

PieCtrlRegs.PIEIER2.all &= MG1_1; // Set "group" priority

PieCtrlRegs.PIEACK.all = 0xFFFF; // Enable PIE interrupts

asm(" NOP"); // Wait one cycle

EINT; // Clear INTM to enable interrupts

*/

volatile uint16_t temPIEIER = HWREGH(PIECTRL_BASE + PIE_O_IER2);

IER |= M_INT1;

IER &= MINT1;

//

// Run the FSK Correlation Detector Function

//

FSK_CORR_DETECTOR_OverSampl_RUN(&FSK_struct1);

//

// See if a mark or space bit is detected

//

if(FSK_struct1.bit_detected != 0)

{

rxMessage[message_index++] = FSK_struct1.bit_detected; // Save the detected bit in the message buffer

FSK_struct1.bit_detected = 0; // Clear the detected bit member

//

// Set flags when message buffer is full

//

if(RX_MESSAGE_SIZE <= message_index)

{

message_index = 0;

msgFull = 1;

}

}

//

// Clear INT flag for EPwm2

//

//EPwm2Regs.ETCLR.bit.INT = 1;

EPWM_clearInterruptStatus(PLC_BITDECTION_EPWM_BASE, ADC_INT_NUMBER2);

//

// Acknowledge this interrupt to receive more interrupts from group 3

//

//PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP3);

//

// Restore registers saved for ADC ISR Nesting

//

DINT;

//PieCtrlRegs.PIEIER2.all = temPIEIER;

HWREGH(PIECTRL_BASE + PIE_O_IER2) = temPIEIER;

//

// Toggle gpio pin for measuring frequency, debug purposes

//

//GpioDataRegs.GPCTOGGLE.bit.GPIO65 = 1; // LP Pin 47

}

Other question. It TI demo code, it is use "EPwm2Regs.ETCLR.bit.INT = 1;" to clear the flag. However, I can't find a driverlib command to do it. Please advice how to do it.

BR

HK Woo

HK,

I'm going to need some more time to debug this; I had added the new EABI lib to the Rx CCS project for F28004x(in C2000Ware( and it compiled without issue. Let me see if I can find those functions and if they still have the "_" populated.

Will look into your other issues as well. I'll give another update tomm afternoon US Central time.

Best,

Matthew

Matthew

Thanks for your respond. My project is running out of time. I am under high pressure on it. Please help to fix it and provide a stable release of library.

It is grant to hear TI will have a demo code in driverlib instead of bitfield. It is more easy for user to use it since TI is recommend to use driverlib instead of bitfield per my understanding.

If possible please share the demo code in driverlib to me in advance. It is no need to waiting for the library.

HK,

I found the issue you were talking about in the library. I'm attaching a corrected version that should resolve the symbol mismatch.

For the Interrupts/PIE I would take a look at the example here: C:\ti\c2000\C2000Ware_3_04_00_00\driverlib\f28002x\examples\interrupt

These are defined in the driver lib interrupt.c here: C:\ti\c2000\C2000Ware_3_04_00_00\driverlib\f28002x\driverlib

For the ETCLR, I believe that this command is what you want EPWM_clearEventTriggerInterruptFlag(myEPWM2_BASE);

Best,

M5861.fsk_corr_detect_lib_eabi.libatthew

HK,

You'll need to add a line to your .cmd file and replace the RAM block # I've defined with whatever section has room: If you are using the generic .cmd from our examples you can use the below as is assuming there is enough room(the linker will let you know if not).

fsk_corr_lib_data : > RAMLS4567 PAGE = 1 /* Ram block for lib data */

Best,

Matthew

Hi Matthew

I have a question on ISR below which is demo code

#pragma CODE_SECTION(epwm2_isr,".TI.ramfunc");

__interrupt void epwm2_isr(void)

{

EALLOW;

//

// Enable ADC ISR Nesting

//

uint16_t TempPIEIER;

TempPIEIER = PieCtrlRegs.PIEIER2.all;

IER |= M_INT1;

IER &= MINT1; // Set "global" priority

PieCtrlRegs.PIEIER2.all &= MG1_1; // Set "group" priority

PieCtrlRegs.PIEACK.all = 0xFFFF; // Enable PIE interrupts

asm(" NOP"); // Wait one cycle

EINT; // Clear INTM to enable interrupts

I am using EPWM3 timer for ISR "adc_sample"_signal and EPWM4 timer for ISR "epwm2_isr".

1. Should I change the below parameters in RED to other values since EPWM4 is using

IER |= M_INT1;

IER &= MINT1; // Set "global" priority

PieCtrlRegs.PIEIER2.all &= MG1_1; // Set "group" priority

2. Below is contents of my .cmd, Could our advise that how to add "fsk_corr_lib_data : > RAMLS4567 PAGE = 1 /* Ram block for lib data */ to it.

MEMORY

{

BEGIN : origin = 0x080000, length = 0x000002

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* RAMLS4 : origin = 0x0000A000, length = 0x00000800

RAMLS5 : origin = 0x0000A800, length = 0x00000800

RAMLS6 : origin = 0x0000B000, length = 0x00000800

RAMLS7 : origin = 0x0000B800, length = 0x00000800*/

/* Combining all the LS RAMs */

RAMLS4567 : origin = 0x0000A000, length = 0x00002000

RAMGS0 : origin = 0x0000C000, length = 0x000007F8

// RAMGS0_RSVD : origin = 0x0000C7F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

// FLASHBANK1 : origin = 0x00080000, length = 0x0000FFF0

// FLASH_BANK1_RSVD : origin = 0x0008FFF0, length = 0x00000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

BOOTROM : origin = 0x003F0000, length = 0x00008000

BOOTROM_EXT : origin = 0x003F8000, length = 0x00007FC0

RESET : origin = 0x003FFFC0, length = 0x00000002

/* Flash sectors */

/* BANK 0 */

FLASH_BANK0_SEC0 : origin = 0x080002, length = 0x000FFE /* on-chip Flash */

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC8_9_10 : origin = 0x088000, length = 0x003000 /* on-chip Flash */

//FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000 /* on-chip Flash */

//FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000 /* on-chip Flash */

//FLASH_BANK0_SEC8_9: origin = 0x088000, length = 0x002000 /* on-chip Flash */

//FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x000FF0 /* on-chip Flash */

// FLASH_BANK0_SEC15_RSVD : origin = 0x08FFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

}

SECTIONS

{

codestart : > BEGIN, ALIGN(8)

.text : >> FLASH_BANK0_SEC2 | FLASH_BANK0_SEC3 | FLASH_BANK0_SEC4 | FLASH_BANK0_SEC5, ALIGN(8)

.cinit : > FLASH_BANK0_SEC1, ALIGN(8)

.switch : > FLASH_BANK0_SEC1, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

.init_array : > FLASH_BANK0_SEC1, ALIGN(8)

.bss : > RAMLS4567

.bss:output : > RAMLS4567

.bss:cio : > RAMGS0

.const : > FLASH_BANK0_SEC1, ALIGN(8)

.data : > RAMLS4567

.sysmem : > RAMLS4567

ramgs0 : > RAMGS0

/* Allocate IQ math areas: */

IQmath : > RAMLS4567

IQmathTables : > RAMLS4567

GROUP

{

.TI.ramfunc

{

-l sfra_f32_tmu_eabi.lib

}

ramfuncs

} LOAD = FLASH_BANK0_SEC6,

RUN = RAMLS4567,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(4)

/*

.TI.ramfunc : LOAD = FLASH_BANK0_SEC1,

RUN = RAMGS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

*/

SFRA_F32_Data : > RAMLS4567, ALIGN = 64

FPUmathTables : > FLASH_BANK0_SEC11

//.scratchpad : > RAMLS4567

//controlVariables : > RAMLS4567

GROUP

{

isrcodefuncs

dclfuncs

} LOAD = FLASH_BANK0_SEC8_9_10,

RUN = RAMLS4567,

LOAD_START(isrcodefuncsLoadStart),

LOAD_SIZE(isrcodefuncsLoadSize),

LOAD_END(isrcodefuncsLoadEnd),

RUN_START(isrcodefuncsRunStart),

RUN_SIZE(isrcodefuncsRunSize),

RUN_END(isrcodefuncsRunEnd),

ALIGN(4)

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

BR

HK Woo

Using an updated lib and no error found during compile. However, I can't get the PLC message on rx_message variable which is always 0. I use scope to check a PLC signal which connected to ADCC module. Hardware signal is ok. I checked the value of variable "input" which is sampling value of PLC signal and found that it changes all the time follow PLC signal from 0.6 to 1.6V. It means ADC sample is OK and confirmed that it is running @ 300K Hz. I checked 586K Hz ISR is running as well. I have tried to change FSK_BIT_DETECTION_THRESHOLD with different value from 0.1 to 0.9. still doesn,t work.I am not sure the library is functional or not

Do you have a demo code running in C2000Ware driverlib on Launchxl-F280049C so that I can test the latest library with LaunchX1-F280049C and Boostxl-AFE031-DF1 together.

I attached my project. Basically, below functions are related to PLC setup

1. config_AFE031();

2. PLC_ADC_Setup();

3. PLC_BitDetection_Setup();

Below are ISR

1. PLC_BITDETECT_ISR @ 586K

2. PLC_ADC_ISR @ 300K

For timeout. I am using my own polling function to check time out.

Please help on it.

BR

HK Woo3771.zip

Hi Matthew

I found that there is a funny thing. rx_message received some wrong data after I changed the marco below

#define SCALE_ADC_INPUT(adc_input) (((float)(adc_input))*ADC_PU_SCALE_FACTOR)*2.0 ->

#define SCALE_ADC_INPUT(adc_input) (((float)(adc_input))*ADC_PU_SCALE_FACTOR)*20.0

and 300Hz ISR stops running after a while.

BR

HK Woo

HK,

Sorry about the delay. I had to get the AFE031 Booster Packs from another C2000 team member. I'll try and hook this up with my launchpads and have a look. I'll likely need another day to get things running on my end so I'll try and give another update tomm.

Can you give some more info on your last update? Were you able to get the libs working, at least for a little while?

Best,

Matthew

Yes. I can got some data after change the factor and the threshold to 0.00xx

Hi Matthew

I found that the 300K ISR stop running is due to the function FSK_CORR_DETECTOR_RUN(input); The ISR keeps running after I commented the function.

BR

HK Woo

Hi Matthew

I am using F280025C in my project. Please be informed about it.

BR

HK Woo

HK,

I confirmed that the new EABI lib is not the issue, I substituted it into the RX example we have in C2000Ware and tested it with another LP/AFE using our TX example and was able to detect and decode the packets correctly.

Are the signals you are generating into the AFE031 similar to those we have in our TX example, or are they of a different frequency and/or amplitude?

From a HW perspective the ADC input on J3-29 is different on the LAUNCHXL-F28002x vs the LAUNCHXL-F28004x. The 28004x example is using ADCINA9, you'll need to change this to either ADCINA12 or ADCINC1. A12 would be simpler since you could keep the ADC config for ADCA that is in the org source

I'm going to look at your code shortly; I'll reply back tonight if I see anything.

Best,

Matthew

Hi Mattew

Thanks for your information. Could you share your RX example to me?

Hi Matthew

For your information, my project use ADCA and ADCC. ADCA is for digital buck converter and ADCC is for PLC sample.

If you don't mind, we can have zoom call.

HK,

I was coming to the same conclusion, that you are using the other BP header for the AFE031 Booster pack.

You will need to re-map both the ADC channel as well as the SPI from the existing examples in order to configure the AFE031 using our example code. Potentially you will need to use another PWM as the ISR time base, since I'm assuming PWM1 is used by the BUCK.

I'm not seeing the afe031_config.c and .h files in the project you attached. This contains the functions to set the AFE031 in the correct mode to receive data properly. Let me know if you've taken care of this inline.

I'm just using the boostxl_afe031_f28004x_rx project right now. I realize that there needs to be some changes to accommodate the F28002x, but I don't its going to be much more than pin mux assignments, and potentially module changes (like we have to use SPI B vs SPI A), etc.

Can you confirm your plugging the AFE031-BOOSTXL, into the bottom pins on the LP?

Best,

Matthew

Hi Matthew

I am not using AFE031-BOOSTXL board. Our company design our own board. The board contains F280025C and AFE031. F280025C has 2 functions digital buck control and PLC communication.

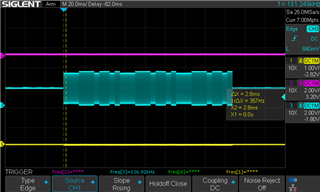

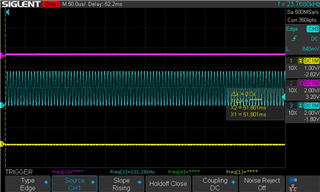

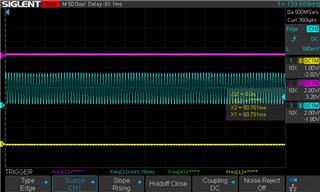

I haven't use TI afe031_config.c and .h in my project. I am using my own code for SPI communication. I confirmed that communication between AFE031 and F280025C is OK. Please find attached waveform, channel 3 (blue) is output of AFE031 pin Rx_PGA2_OUT which connected to F280025C ADC_CH_ADCIN3. The waveform shows that PLC signal is correct. 143.75K Hz and 131.25K Hz

The problem I had is that why 300K ISR stop running after a while. If I comment FSK_CORR_DETECTOR_RUN in ISR PLC_ADC_ISR(), 300K ISR keep running. I measured the process time for the PLC_ADC_ISR(). It is 2.5us max. It will not cause any over running because 300K is ~ 3.3us. Is it still to wrong Interrupt configuration in my code?

BR

HK Woo

HK,

I need to check if the ISR timing is different than the COFF based version. The FSK_CORR_DETECTOR_RUN function is written in assembly so the typical challenges of moving from COFF to EABI, that is the float and double casts being different shouldn't apply. I'll see if I can get the code author of this to comment as well.

I'll attempt to run both the COFF and EABI versions in the lab tomorrow as well. As you said even though the over-run is OK, there is only 1us of BW left.

Best,

Matthew

HK,

I verified that the cycle counts are consistent across the EABI and COFF variants of the FSK lib. I was looking at your project again, and I think there may be some memory conflicts that could contribute to FSK_CORR_DETECTOR_RUN function taking longer than expected. The function itself should take 59 CPU cycles, or 590ns at 100MHz clock.

I noticed in the linker command file that ships with the AFE examples we have partitioned the Sine Table and fsk_corr_lib in separate memories from each other, as well as separate from the other memories. I realize not all these memories are available on the F28002x, in addition to you have buck controller code that must co-exist. Even if the above share some space with the main code, if we could partition such that the sine table and fsk_lib are not in the same physical block that would be good.

I also realize that I previously mentioned to place the LIB in the "combined" LS# block type configuration, apologies on that aspect earlier.

{

codestart : > BEGIN, PAGE = 0

.TI.ramfunc : > RAMM0 PAGE = 0

.text : >>RAMM0 | RAMLS0 | RAMLS1 | RAMLS2 | RAMLS3, PAGE = 0

.cinit : > RAMLS2, PAGE = 0

.init_array : > RAMM0, PAGE = 0

.switch : > RAMM0, PAGE = 0

.cio : > RAMLS0, PAGE = 0

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

.stack : > RAMM1, PAGE = 1

.bss : > RAMLS6, PAGE = 1

.const : > RAMLS6, PAGE = 1

.sysmem : > RAMLS6, PAGE = 1

ramgs0 : > RAMGS0, PAGE = 1

ramgs1 : > RAMGS1, PAGE = 1

SINETABLE : > RAMGS2, PAGE = 1 /* Ram block for SINETABLE data */

fsk_corr_lib_data : > RAMGS3, PAGE = 1 /* Ram block for lib data */

FlashAPIDataSection : > RAMM1, PAGE = 1, ALIGN(4)

}Let me know if this is possible and if it brings the ISR time down, etc.

Best,

Matthew

Hi Matthew

I am not unfamiliar with the linker file. I just use a example from demo code. Please advise how to optimize it.

Furthermore,

I still can't use bitfield to set register bit in my project (don't know the reason). I would like to set follow bit

1.ADCC Register -> ADCINTSEL1N2 -> INT2CONT

2.ADCC Register -> ADCINTSEL1N2 -> INT1CONT

3.ADCC Register -> ADCINTSEL3N4 -> INT4CONT

4.ADCC Register -> ADCINTSEL3N4 -> INT3CONT

Please advise how to do it using driverlib

BR

HK Woo

HK,

For the Continuous mode for the ADC Int, use this function https://dev.ti.com/tirex/explore/content/tirex-product-tree/C2000Ware_3_04_00_00_Device/device_support/f28002x/docs/html/modules/adc.html#_CPPv424ADC_enableContinuousMode8uint32_t13ADC_IntNumber

for example for the first of the 4 it would be

ADC_enableContinuousMode(ADC_ADCC, ADC_INT_NUMBER2)

I need a bit more time to look at your memory allocation(I have it in your project from before) to see what changes can be made.

Best,

Matthew

I tried the command. It wouldn’t change the bit. I checked the bit value with view->register in CCS

HK,

For the continuous mode I thought the ADC_ADCC was the defined base, it should have been:

ADC_enableContinuousMode(ADCC_BASE, ADC_INT_NUMBER2);

There is an example in C2000Ware that shows the use of this function here

C:\ti\c2000\C2000Ware_3_04_00_00\driverlib\f28002x\examples\adc\CCS\adc_ex5_soc_continuous.projectspec

For the linker file let's bring LS6 and LS7 back out of the large block like below(you can leave everything after this line the same for the memory section:

MEMORY

{

BEGIN : origin = 0x080000, length = 0x000002

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* Combining the LS RAMs 4 and 5*/

RAMLS45 : origin = 0x0000A000, length = 0x00001000

RAMLS6 : origin = 0x0000B000, length = 0x00000800

RAMLS7 : origin = 0x0000B800, length = 0x00000800

RAMGS0 : origin = 0x0000C000, length = 0x000007F8

// RAMGS0_RSVD : origin = 0x0000C7F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

For the allocations change as below:

SECTIONS

{

codestart : > BEGIN, ALIGN(8)

.text : >> FLASH_BANK0_SEC2 | FLASH_BANK0_SEC3 | FLASH_BANK0_SEC4 | FLASH_BANK0_SEC5, ALIGN(8)

.cinit : > FLASH_BANK0_SEC1, ALIGN(8)

.switch : > FLASH_BANK0_SEC1, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

.init_array : > FLASH_BANK0_SEC1, ALIGN(8)

.bss : > RAMLS45

.bss:output : > RAMLS45

.bss:cio : > RAMGS0

.const : > FLASH_BANK0_SEC1, ALIGN(8)

.data : > RAMLS45

.sysmem : > RAMLS45

ramgs0 : > RAMGS0

/* Allocate IQ math areas: */

IQmath : > RAMLS45

IQmathTables : > RAMLS45

GROUP

{

.TI.ramfunc

{

-l sfra_f32_tmu_eabi.lib

}

ramfuncs

} LOAD = FLASH_BANK0_SEC6,

RUN = RAMLS67,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(4)

/*

.TI.ramfunc : LOAD = FLASH_BANK0_SEC1,

RUN = RAMGS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

*/

SFRA_F32_Data : > RAMLS45, ALIGN = 64

FPUmathTables : > FLASH_BANK0_SEC11

//.scratchpad : > RAMLS4567

//controlVariables : > RAMLS4567

GROUP

{

isrcodefuncs

dclfuncs

} LOAD = FLASH_BANK0_SEC8_9_10,

RUN = RAMLS45,

LOAD_START(isrcodefuncsLoadStart),

LOAD_SIZE(isrcodefuncsLoadSize),

LOAD_END(isrcodefuncsLoadEnd),

RUN_START(isrcodefuncsRunStart),

RUN_SIZE(isrcodefuncsRunSize),

RUN_END(isrcodefuncsRunEnd),

ALIGN(4)

}Hi Matthew

Thanks for your information. I still have 2 questions.

1. I am still not sure the configuration on 586Hz ISR, Interrupt setting is same as the one on TI demo code. I highlight in RED.

interrupt void PLC_BITDETECT_ISR(void)

{

//

// Enable ADC ISR Nesting

//

volatile uint16_t tempPIEIER = HWREGH(PIECTRL_BASE + PIE_O_IER2);

// GPIO_togglePin(DEBUG_GPIO);

IER |= M_INT1;

IER &= MINT1;

HWREGH(PIECTRL_BASE + PIE_O_IER2) &= MG1_1;

Interrupt_clearACKGroup(0xFFFFU);

//EPWM_clearEventTriggerInterruptFlag(PLC_BIT_DETECT_EPWM_BASE);

//Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP3);

//TempPIEIER = PieCtrlRegs.PIEIER2.all;

//IER |= M_INT1;

//IER &= MINT1; // Set "global" priority

//PieCtrlRegs.PIEIER2.all &= MG1_1; // Set "group" priority

//PieCtrlRegs.PIEACK.all = 0xFFFF; // Enable PIE interrupts

asm(" NOP"); // Wait one cycle

EINT; // Clear INTM to enable interrupts

//

// Run the FSK Correlation Detector Function

//

FSK_CORR_DETECTOR_OverSampl_RUN(&FSK_struct1);

//

// See if a mark or space bit is detected

//

if(FSK_struct1.bit_detected != 0)

{

rxMessage[message_index++] = FSK_struct1.bit_detected; // Save the detected bit in the message buffer

FSK_struct1.bit_detected = 0; // Clear the detected bit member

//

// Set flags when message buffer is full

//

if(RX_MESSAGE_SIZE <= message_index)

{

message_index = 0;

msgFull = 1;

}

}

//

// Clear INT flag for EPwm2

//

//EPwm2Regs.ETCLR.bit.INT = 1;

EPWM_clearEventTriggerInterruptFlag(PLC_BIT_DETECT_EPWM_BASE);

//

// Acknowledge this interrupt to receive more interrupts from group 3

//

//PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP3);

//

// Restore registers saved for ADC ISR Nesting

//

DINT;

//PieCtrlRegs.PIEIER2.all = TempPIEIER;

HWREGH(PIECTRL_BASE + PIE_O_IER2) = tempPIEIER;

//GPIO_togglePin(DEBUG_GPIO);

}

2. Our product is going to application IEC60730. Does the library are IEC60730? If not, I need to know how to define address RAM manually instead of do by compiler.

BR

HK Woo

Hi HK, Matt is out of the office. I'll try to ID another subject matter expert to help, but even so it may be Tuesday until you receive a reply.

Hi HK,

For #1, see the documentation below for interrupt nesting.

https://software-dl.ti.com/C2000/docs/c28x_interrupt_nesting/html/index.html

For #2 IEC60730 was not a requirement when the library was written, so I don't believe it meets the safety standard by default.

Best,

Kevin